Intel: ALTPLL のロケーションを手動で指定する方法を教えてください。

カテゴリー:Tool

ツール:Quartus® Prime Standard Edition、Quartus® Prime Lite Edition

デバイス:Cyclone® 10 LP、Cyclone® IV、MAX® 10

ALTPLL のロケーションを手動でおこなうには、Assignment Editor を使用します。

各項目へ指定する内容は、下表のとおりです。

| To 欄 | ALTPLL のノード名

※ To 欄に指定する ALTPLL のノード名は Locked 出力信号の使用の有無 で異なります。表下の情報を参考に設定してください。 |

| Assignment Name 欄 | Location |

| Value 欄 | 配置させる位置情報を指定 Element: PLL Location: PLL_<number> |

▶ Locked 出力信号を使用している場合

| To 欄で選択するノード名 |

| <pll name>:<instance name>|altpll:altpll_component|pll_altpll:auto_generated|pll1 |

| 指定方法の一例 |

|

Assignment Editor の Node Finder で上記ノード名を検索します。

|

▶ Locked 出力信号を使用していない場合

※ Locked を使用していない場合は、上記の Locked 出力信号を使用している場合 の方法でも指定可能です。

| To 欄で選択するノード名 |

| <pll name>:<instance name> |

| 指定方法の一例 |

|

Quartus® Prime の Project Navigator から ALTPLL IP を右クリック選択 > Locate Node > Locate in Assignment Editor を選択し、To 欄から指定した PLL 名を選択します。(下図参考)

|

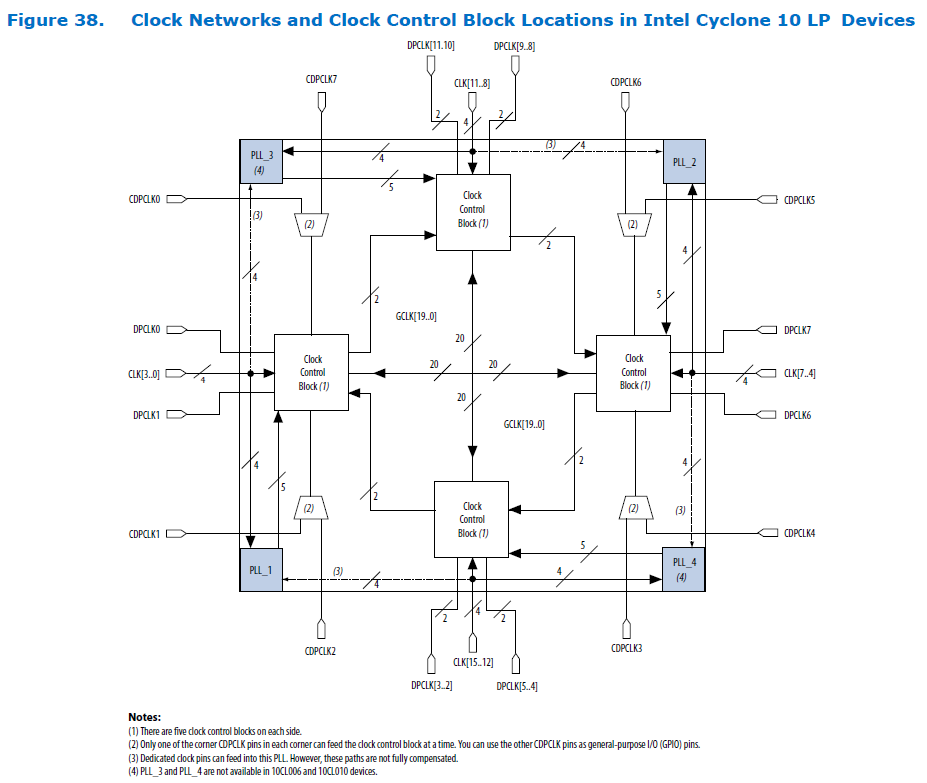

なお、ALTPLL に対応した FPGA シリーズにおいて、PLL リファレンスクロックピンのレイアウトと PLL のロケーションには相関関係があります。(下図参照)

配置を指定した PLL へリファレンスクロックピンがダイレクトに接続できない場合には、クロックコントロールブロックを経由して接続されますので、クロックパスの遅延が増加します。

一方、リファレンスクロックピンからダイレクトに配線された PLL であっても、FPGA ファミリーにより補正が保証されていないパスがありますので、必ずターゲットデバイスのハンドブックを参照してください。

なお、PLL Intel FPGA IP (旧 Altera PLL) のロケーションを手動で指定する方法は、こちら の FAQ をご覧ください。