Intel:PLL Intel FPGA IP のロケーションを手動で指定する方法を教えてください。

カテゴリー:Device

ツール:Quartus® Prime Standard Edition、Quartus® Prime Lite Edition

デバイス:Stratix® V、Arria® V、Cyclone® V

PLL Intel FPGA IP のロケーションを手動でおこなうには、Assignment Editor を使用します。

|

To 欄 |

PLL Intel FPGA IP のノード名 |

|

Assignment Name 欄 |

Location |

|

Value 欄 |

配置させる位置情報 |

Value 欄で選択する Element 名により、選択するノード名が異なります。

下表を参考に、いずれかの制約で PLL のロケーションを設定してください。

|

オススメ |

To 欄で選択するノード |

Value 欄で選択する Element 名 |

Value 欄で指定する配置 |

||

|

X |

Y |

Z |

|||

|

★ |

*|altera_pll:altera_pll_i|general[0].gpll~FRACTIONAL_PLL |

Fractional PLL |

Device Handbook の PLL Locations で確認できる数値を指定 |

Device Handbook の PLL Locations で確認できる数値を指定 |

0 |

|

*|altera_pll:altera_pll_i|general[0].gpll~PLL_REFCLK_SELECT |

PLL Reference Clock Select Block |

Device Handbook の PLL Locations で確認できる数値を指定 |

Chip Planner などで確認する必要あり |

0 |

|

|

*|altera_pll:altera_pll_i|general[0].gpll~PLL_RECONFIG |

PLL Reconfiguration Block |

Device Handbook の PLL Locations で確認できる数値を指定 |

Chip Planner などで確認する必要あり |

0 |

|

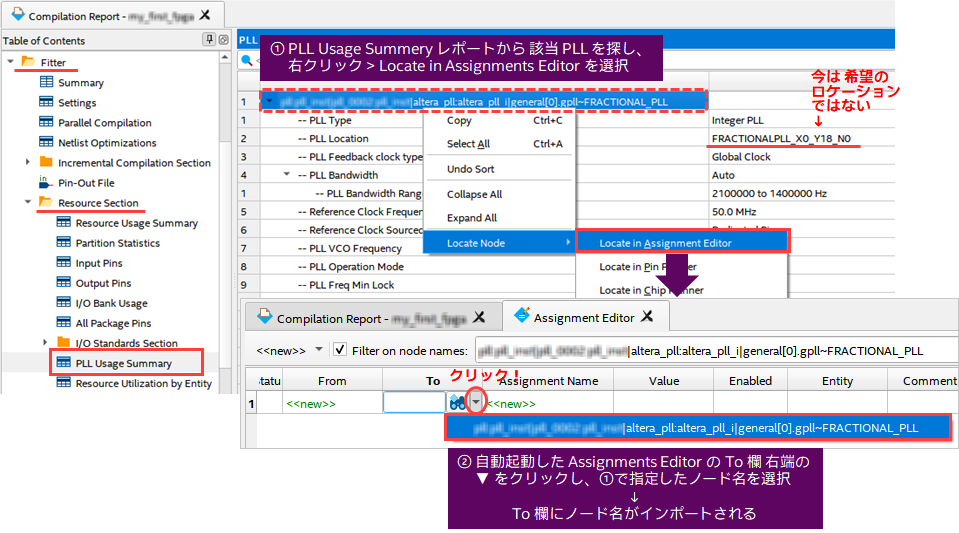

また、PLL のノード名の指定方法には、Assignment Editor の Node Finder で検索する方法の他に、一度 暫定でフィッティングをさせ、コンパイルレポートからノード名を選択して Assignment Editor でロケーション指定する方法もあります。(下図参照)

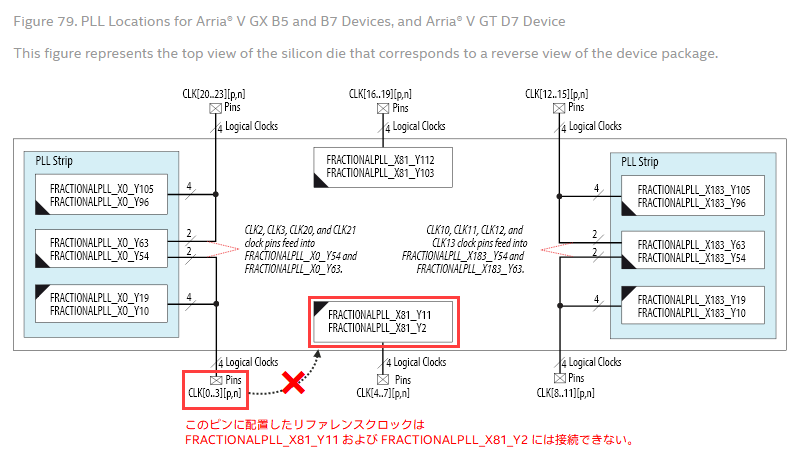

なお、V シリーズの FPGA 内蔵の PLL は、PLL リファレンスクロックピンのレイアウトと PLL のロケーションに相関関係があります(下図参照)。デバイスの構造により クロックピンに接続されていない PLL へは、ロケーションを指定しても配置させることができません。

例: Arria® V GX B5 and B7 Devices, and Arria® V GT D7 Device PLL Locations