はじめに

現代の電子機器において、正確かつ効率的なクロック生成は、システムの性能と信頼性を大きく左右する要素です。

この重要な役割を担う中で、スカイワークス社のクロック製品は特に注目に値します。

スカイワークス社のクロック製品は、低ジッタかつ柔軟に周波数のカスタマイズが可能であり、様々なクロックフォーマットにも対応しているため、

通信システムや精密なデータ処理が求められる製品での使用に適しています。

また、部品集約やBOMコストの削減、実装面積の縮小といった経済的なメリットも提供可能なので、製品設計者にとって大きな利点となります。

この記事では、スカイワークス社のクロック製品がいかにしてこれらの特長を実現しているのか、その背後にある3つの特徴的な技術について解説します

FPGA、SoC、CPUなどの制御デバイスとの相性がよく、周辺デバイスとして安心して利用可能なスカイワークス社のクロック製品について知っていただき、検討の一つとしていただければと思います。

スカイワークス社クロック製品の特徴的な3つの技術とは?

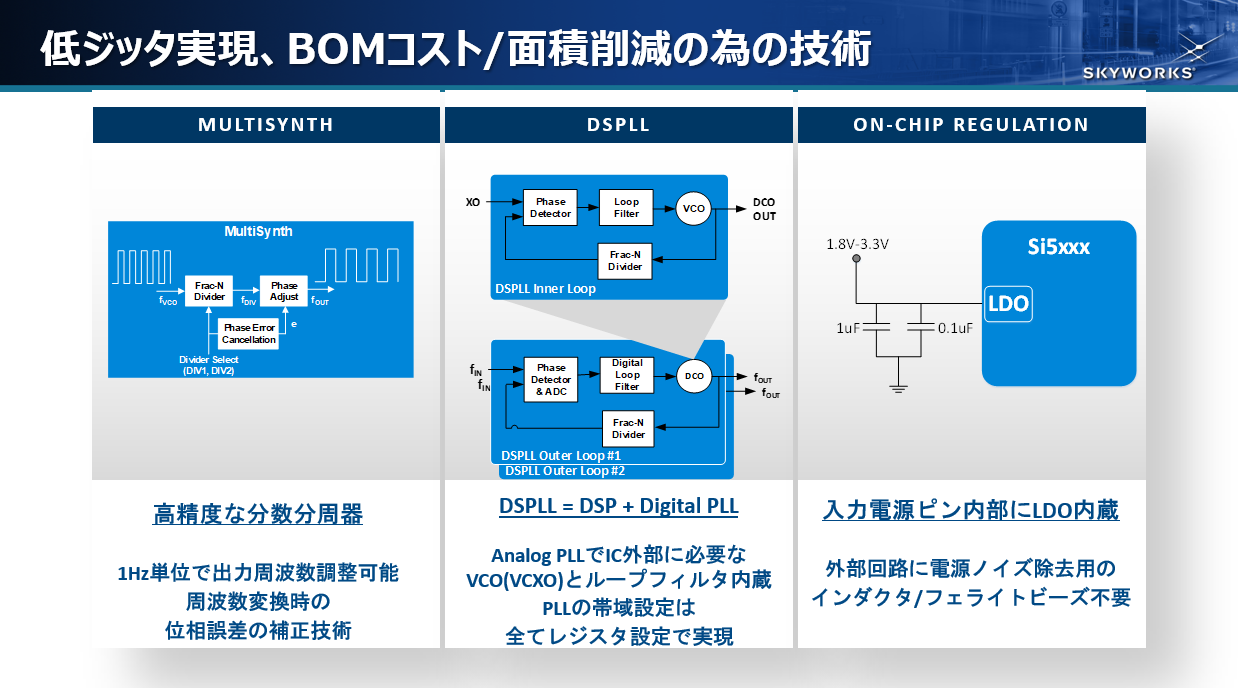

低ジッタ実現、BOMコスト/面積削減の為のスカイワークス社独自の3つの技術として、「MultiSynth(マルチシンセ)」、「DSPLL」、「On-Chip Regulation」があります。

以下の図は、3つの技術の概要になります。次項で順にご説明します。

MultiSynth技術

スカイワークス社独自の技術であり、このMultiSynth技術によって高精度/高分解能の周波数設定が可能です。具体的には、MHzオーダーで小数点第6桁(1.000000MHz、つまり1Hz単位)の周波数設定が可能、かつ、0ppmで位相誤差なく同期した出力ができる優れた技術となっています。

そして、一般的な分周器の特性として、Integerに比べ、Fractionalで分周した場合、ジッターパフォーマンスが悪化する傾向にありますが、MultiSynthでは内部に周波数変更時の位相ずれを調整する機能ブロックを有しており、さほどジッタパフォーマンスが劣化しない特長を持ちます。

この技術が搭載されているデバイス例として、Si5391やSi5332などのクロックジェネレーターがあげられます。

クロック周波数例:ビデオ信号 148.5MHz/1.001=148.351648MHz

イーサネット 161.132812MHz など

下図にMultiSynthのブロック図を示します。

MultiSynthに関する詳細はこちらから

DSPLL

DSPLLは、DSP(Digital Signal Processor)とPLLが合わさったスカイワークス社の造語になります。

1つのPLLにもう一つ入れ子として、PLLが内蔵されており、より入力信号のジッタを低減させる働きをします。

アナログLC-VCOとDSPベースのデジタルループフィルターおよびデジタル位相検出器を組み合わせています。

このように、従来のアナログPLLのIC外部に必要なVCO(VCXO)やループフィルタは、1つのDPLLに内蔵されている為、部品点数の削減や実装面積の縮小につながります。

また、ジッタ減衰以外にもDSPLL搭載デバイスの中には、任意の周波数変換(FOTF)やヒットレススイッチング、ホールドオーバー機能を持ち、PLLの帯域設定は全てレジスタ設定で実現可能です。

この技術が搭載されているデバイス例として、スカイワークス社の水晶発振器(XO、VCXO)とSi5392/4/5やSi5396/7などのジッタアッテネーターがあげられます。

引用元:「Innovative DSPLL® and MultiSynth Clock Architecture」(p.4: Figure 2. Skyworks’ Fourth-Generation DSPLL Architecture vs. Traditional Approach)

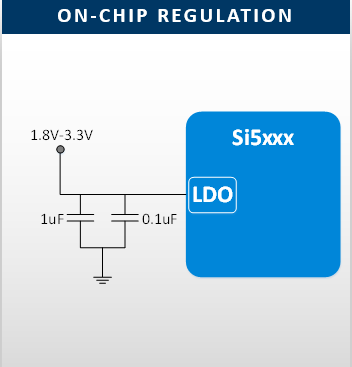

On-Chip Regulation

Si5xxxから始まる型番には、チップの入力電源ピン内部にLDOが内蔵されています。出力のドライバ側にも各出力ピン毎にLDOが内蔵されている為、クロストークを軽減する働きをします。

また、電源ライン部のノイズ対策として、外部回路に電源ノイズ除去用のインダクタやフェライトビーズは不要なので、部品点数の削減や実装面積縮小につながります。

関連資料

Whitepaper

お問い合せ

本製品に関するお問い合わせは、以下のボタンをクリックしてください。

スカイワークス社メーカ情報Topへ

スカイワークス社のメーカー情報Topページに戻りたい方は以下をクリックください。