製品概要

Micron Technology社 DDR5 SDRAM製品は、DDR4と比較して利用可能帯域幅が最大2倍となり、転送速度 6400MT/Sを実現します。

従来抱えていたメモリーアクセスのボトルネックを解消することで、AIの学習や推論、生成AI、データ分析等のアプリケーションで求められる大量データアクセスへの対応が可能になります。

製品ラインナップ

|

型名 |

MT60B4G4RZ-56B:D |

MT60B2G8RZ-56B:D |

MT60B1G16HD-56B:D |

|

容量 |

16Gb |

||

|

データ幅 |

x4 |

x8 |

x16 |

|

パッケージ |

78-ball (7.5mm x 11mm) |

78-ball (7.5mm x 11mm) |

102-ball (7.5mm x 14mm) |

|

ス ピ ー ド グ レード |

DDR5-5600(2800MHz), CL = 46 |

||

|

動作温度 |

0℃ to +95℃ (IT 品:-40℃ ~ +95℃はご相談ください) |

||

|

型名 |

MT60B6G4RW-56B:B |

MT60B3G8RW-56B:B |

MT60B1536M16RV-56B:B |

|

容量 |

24Gb |

||

|

データ幅 |

x4 |

x8 |

x16 |

|

パッケージ |

78-ball (8mm x 11mm) |

78-ball (8mm x 11mm) |

102-ball (8mm x 14mm) |

|

ス ピ ー ド グ レード |

DDR5-5600(2800MHz), CL = 46 |

||

|

動作温度 |

0℃ to +95℃ |

||

※表に記載のないスピードグレード、動作温度のデバイスについては個別にお問い合わせください。

DDR5の主な新機能

低電圧化

VDD電圧とVDDQ電圧を低電圧化させることで低消費電力化に貢献しています。

DFE (decision feedback equalizer)

デバイス内部のデータアイを開くことができ、ISI(inter-symbol interference)の影響を軽減することができます。

DCA (Duty cycle adjuster)

読み取り時にDQ/DQSのDuty cycleを調整できる回路で、PCBを通過する際に自然に発生する小さなDuty cycleの歪みを修正し、最終的にコントローラーが受信するDQ/DQS信号のDuty cycleを最適化します。

その他の新機能はこちら

DQS inteval oscillator

電圧/温度変化により引き起こされるDQSクロックツリーの遅延変化をコントローラーにて監視できるようにする回路で、コントローラー設計者は、書き込みタイミングの最適化に再トレーニングが必要かどうかを判断することができます。

新しいトレーニングモード

DDR4で搭載されるwrite leveling training modeに加え、read preamble, command and address, chip selectの training modeを新たに採用し高速なデータ転送を可能にしています。

専用のmode register

専用のmode register に読み取りトレーニングパターンを保有しています。高速なデータ転送においてより堅固なタイミングマージンを提供します。

内部基準電源

command/address及び chip select用の内部基準電源を設置しています。VREFDQに加えVREFCA, VREFCSの内部基準電源により電圧マージンが向上し、より高速なデータ転送を可能にします。

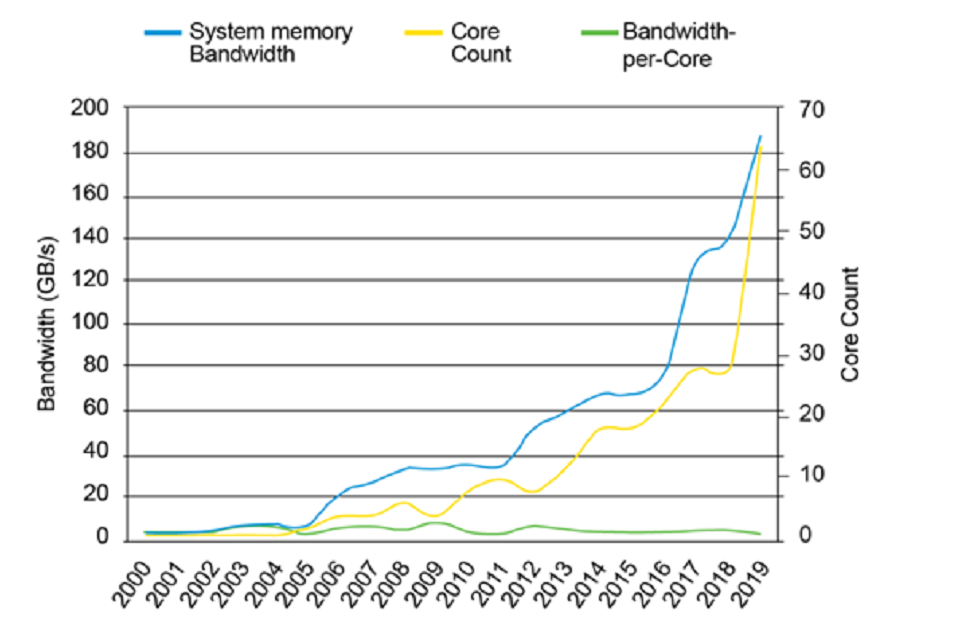

DDR4の課題 マルチコア化による帯域幅拡大

次世代プロセッサーは、搭載コア数を増やして並列処理を可能にすることで、性能向上を実現しています。マルチコア化によりシステムで求められる帯域幅が拡大し、DDR4の転送速度では仕様を満たせないケースが増えました。

以下のグラフでは、一つのコアが必要な帯域幅(緑色のライン)はほぼ一定であるものの、プロセッサーの搭載コア数(黄色のライン)の増加によりシステムとして必要な帯域幅(水色のライン)が拡大しているのが確認できます。

出典: https://assets.micron.com/adobe/assets/urn:aaid:aem:f1706cdb-4b55-4568-84bc-b7ee42f46236/renditions/original/as/ddr5-more-than-a-generational-update-wp.pdf

DDR5は転送速度を向上し、帯域幅の課題を解決

DDR5では転送速度が向上し、規格上ではDDR4 の2倍となる6400MT/Sと定義されています。

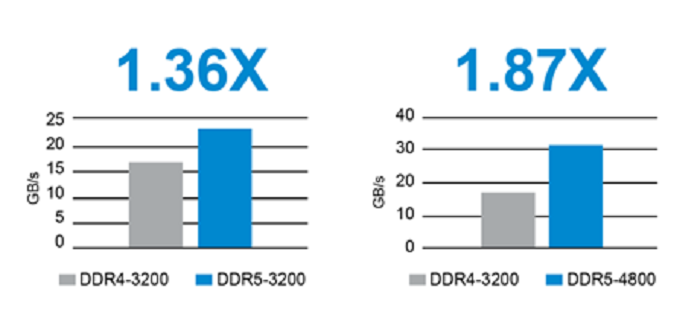

以下の転送速度のシミュレーション結果から、同じ転送速度3200MT/sのDDR4と比べDDR5は帯域幅が1.36倍、DDR4-3200とDDR5-4800では帯域幅が1.87倍になっていることが分かります。

出典: https://assets.micron.com/adobe/assets/urn:aaid:aem:f1706cdb-4b55-4568-84bc-b7ee42f46236/renditions/original/as/ddr5-more-than-a-generational-update-wp.pdf

その他の改善として、電源電圧はDDR4の1.2Vに対して、DDR5では1.1Vと低電圧化され電力効率の向上を図っています。

Burst LengthとBank GroupはDDR4と比べて2倍になり、DDR5は効率的にデータ転送を高速化する工夫がされています。

その他の項目については、以下の製品仕様をご確認ください。

製品仕様

|

製品シリーズ |

DDR4 SDRAM |

DDR5 SDRAM |

|

データ転送速度 |

1600~3200MT/S |

3200~6400MT/S |

|

VDD/VDDQ/VPP |

1.2V/1.2V/2.5V |

1.1V/1.1V/1.8V |

|

内部基準電源 |

VREFDQ |

VREFDQ, VREFCA, VREFCS |

|

コンポーネント容量 |

2-16Gb |

8-64Gb |

|

Prefetch |

8n |

16n |

|

Burst Length |

8 |

16 |

|

Bank groups (BG)/banks |

4 BG x 4 banks |

8 BG x 2 banks (8Gb x4/x8)4 BG x 2 banks (8Gb x16)8 BG x 4 banks (16-64Gb x4/x8)4 BG x 4 banks (16-64Gb x16) |

|

Page size |

512B/1KB/2KB |

1KB/1KB/2KB |

|

One-Die ECC |

× |

〇 |

|

DQ receiver equalization |

× |

Multi-tap DFE |

|

DCA(Duty cycle adjustment) |

× |

DQS and DQ |

|

PRECHARGE commands |

All bank and per bank |

All bank, per bank, and same bank |

|

REFRESH commands |

All bank |

All bank and same bank |

|

Training mode |

write leveling |

write leveling read preamble command and address chip select |

|

Internal DQS delay monitoring |

× |

〇 |

|

Read training patterns |

DDR4: MPRを使用 |

DDR5: 専用Mode Registerを使用 |

|

Package |

78 BGA/96 BGA |

82 BGA/102 BGA |

出典:https://assets.micron.com/adobe/assets/urn:aaid:aem:f1706cdb-4b55-4568-84bc-b7ee42f46236/renditions/original/as/ddr5-more-than-a-generational-update-wp.pdf

お問い合わせはこちら

メーカー参考資料

Introducing Micron DDR5 SDRAM: More Than a Generational Update

関連ページ

- Micron Technology社 DRAM製品ページ

- Micron Technology社 DDR3 SDRAM

- Micron Technology社 DDR4 SDRAM

- Micron Technology社 LPDDR4/4X SDRAM

- Micron Technology社 LPDDR5/5X SDRAM

- DDR4の後方互換性 – 転送速度とレイテンシー(CL, tAA)の確認方法 –

- 押さえておきたいDRAMの基礎 Part 1: 読み書きの原理と内部構造

- 押さえておきたいDRAMの基礎 Part 2: コマンドとシーケンス

- メモリーソフトウェアにご興味のある方はファイルシステムを取り扱っているTuxera製品もご確認下さい