ザインエレクトロニクス株式会社 次世代高速インターフェース標準技術「V-by-One® HS plus Standard」対応FPGA用 IPコア

概要

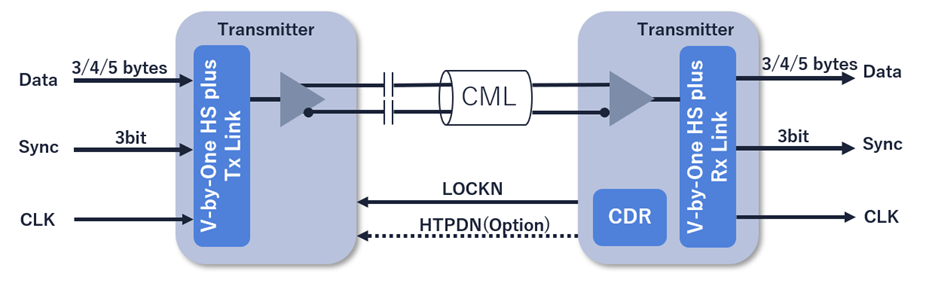

V-by-One® HS plus Tx/Rx IPは、Altera® 社製 FPGAで最新の「V-by-One® HS plus Standard」に対応した信号の送受信を実現するためのIPです。

V-by-One® HS plus Standardの概要

V-by-One® HS plusは、ザインエレクトロニクス株式会社が提唱・策定する次世代高速インターフェース標準技術です。主なポイントは以下の通りです。

- 最大8Gbps/laneの伝送速度

従来技術の2倍の速度で、液晶テレビや有機ELテレビなどの高解像度化やゲーミング用途の高リフレッシュレートをサポートします。 - 省ケーブル化・スリム化

機器内部の伝送路の省ケーブル化・スリム化により、システムコストや消費電力の低減に寄与します。 - 後方互換性の確保

従来のV-by-One® HSとの後方互換性を持つ「HS Mode」と、最大8Gbps/laneでの伝送を可能とする「HS plus Mode」の2種類のモードが定義されています。 - ユーザーの利便性向上

従来のV-by-One® HSの基本プロトコルと設計思想を踏襲し、導入のハードルが低い次世代高速インターフェース標準です。

本IPの特徴

対応構成

- バイトモード

3バイト、4バイト、または5バイトモードをサポートします。 - レーン数

最大32レーンの集約をサポートします。 - 後方互換性

「HS Mode」と「HS plus Mode」のいずれもサポートします。

転送速度

- 最大8.0 Gbps/lane

その他機能

- テストパターンモード

PRBS7、PRBS9、K28.1、およびV-by-One HS plusをサポート - レーン間デスキュー(Rx時)

最大15シンボルクロック

IPリリース予定時期 ( 対応FPGA別 )

Altera® 社製

- Arria® 10 GX FPGA

- Cyclone® 10 GX FPGA

- Agilex™ 7 FPGA ※ F-Tile品でのサポートとなります。

- Agilex™ 5 FPGA ※ 弊社までお問い合わせください。

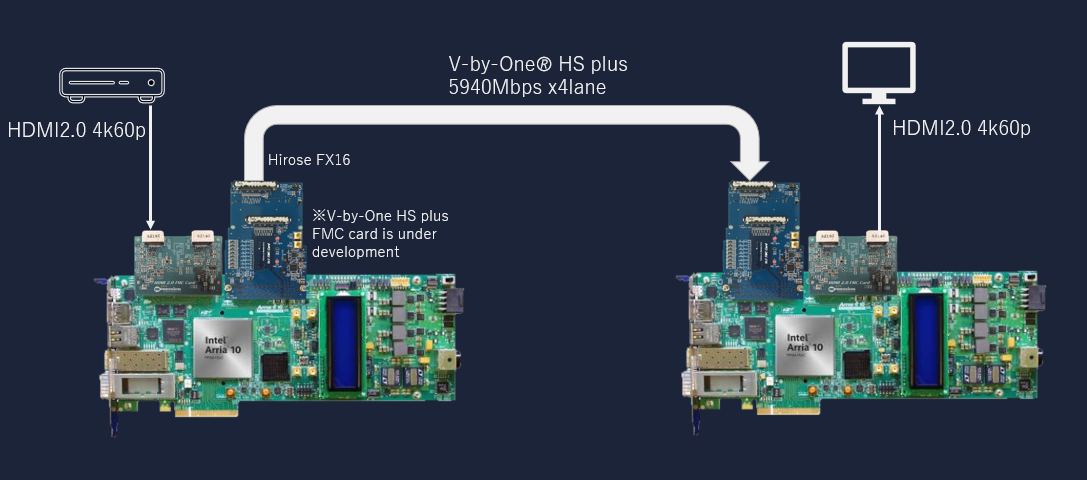

デモ構成例