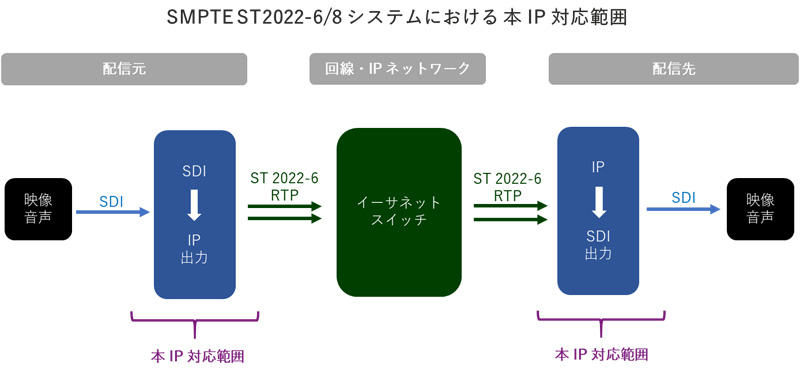

SMPTE® ST2022-6/7/8 規格対応 IP

概 要

SMPTE ST 2022-7 規格にも対応しており、Hitless Protectionによる冗長性のある伝送をおこないます。

※1: Internet Protocol

※2: Intellectual Property

本 IP(※2) は弊社評価キット EASYSS10 Box に適用可能です。適用することでお客様の方では手を加えず、すぐにEASYSS10 Box を ST2022-6/8 SDI/IP Gateway 評価機としてご使用頂けます。

特 長

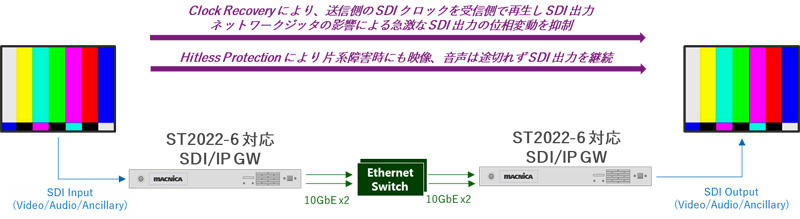

◇ SMPTE ST 2022-6規格に準拠した SDI 信号の IP 伝送

- ST 2059-1/2 PTP グランドマスターを必要としない SDI-IP 伝送が可能

- 送信側 SDI クロックを受信側で再生し SDI 出力。ネットワークジッターの影響による急激な SDI 出力の位相変動を抑制 (Clock Recovery 機能)

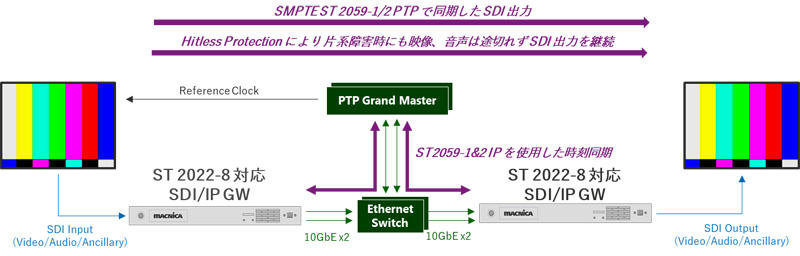

◇ SMPTE ST 2022-8規格に準拠した SDI 信号の IP 伝送

- ST 2059-1/2 による PTP グランドマスターに同期した SDI-IP 伝送が可能

◇ SMPTE ST 2022-7規格に対応

- ネットワークインターフェース2ポートを使用した Hitless Protection による冗長性のある伝送が可能

◇ 最大6 SDI ストリームの同時伝送

- ストリームごとに伝送方式 (ST 2022-6/ST 2022-8) を指定可能

- 入出力SDI フォーマットの自動認識および Resolution やFrame Rate が異なる SDI の混在伝送が可能

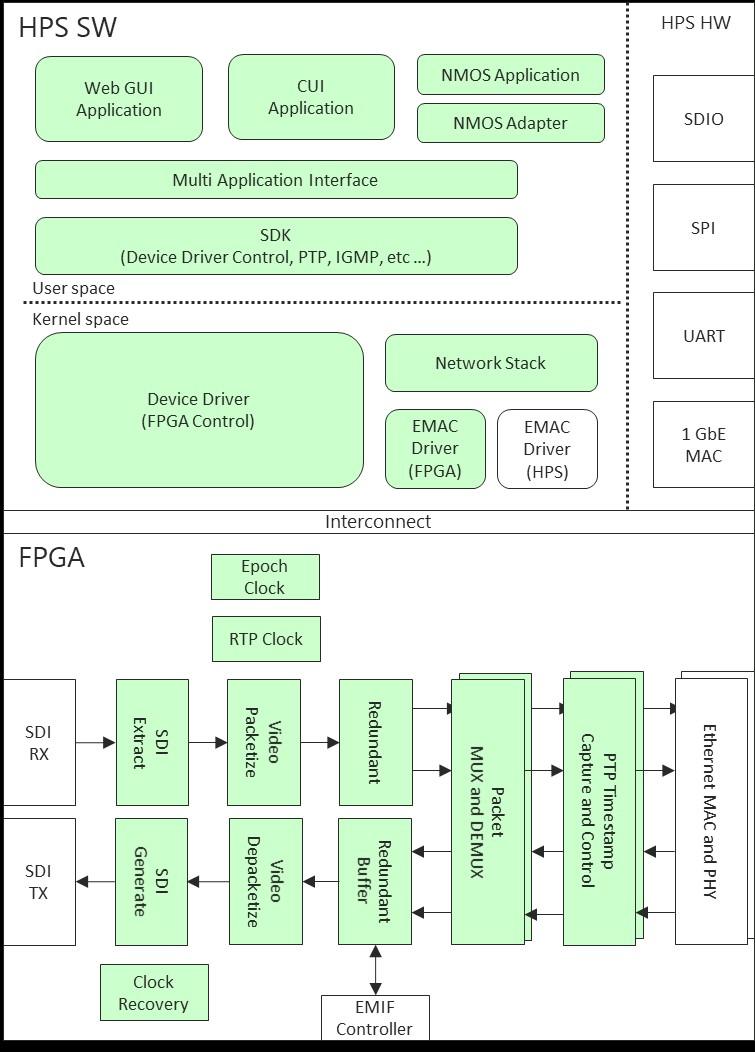

◇ 提供ソフトウェア(SDK)にてAPI を提供

- API 経由で FPGA レジスタ、PTP、IGMP 等の制御が可能。お客様は上位レイヤのソフトウェア開発に注力頂けます。

- リファレンスアプリケーション(Web GUI、CUI) を同梱。ドキュメントとソースコードでAPI の仕様把握が可能。

◇ 通常の IGMP 制御に加えて、ネットワーク使用帯域の超過を防止する IGMP制御機能を搭載 (Bandwidth Exceed Protection オプション)

仕 様

◇ SMPTE® Profile

- ST 2022-6

- ST 2022-7

- ST 2022-8

- ST 2110-10

- ST 2059-1/2

◇ NMOS Profile

- IS-04 ※計画中

- IS-05 ※計画中

◇ SDI フォーマット

- Resolution

1280x720p (HD-SDI), 1920x1080i (HD-SDI), 1920x1080p (3G-SDI)

- Frame Rate

50Hz, 59.94Hz, 60Hz

◇ Ethernet Interface

- 10 GbE x 2

- 25 GbE x 2 ※計画中

◇ IGMP

- IGMP version 2, version 3

アプリケーション例

◇ ST 2022-6 SDI/IP Gateway 適用例

◇ ST 2022-8 SDI/IP Gateway 適用例

対応デバイス

◇ Intel® Arria® 10 SoC

◇ Intel® Arria® 10 GX + NXP® i.MX7D ※計画中

◇ Intel® Stratix® 10 SoC ※計画中

デバイス使用リソース

◇ Device : 10AS066K3F40E2SG

◇ Device : 10AS066K3F40E2SG

◇ Logic utilization (in ALMs) : 122,098 / 251,680 ( 49 % )

◇ Total registers : 244890

◇ Total block memory bits : 7,082,272 / 43,642,880 ( 16 % )

◇ Total RAM Blocks : 714 / 2,131 ( 34 % )

◇ Total DSP Blocks : 5 / 1,687 ( < 1 % )

◇ Total HSSI RX channels : 9 / 36 ( 25 % )

◇ Total HSSI TX channels : 9 / 36 ( 25 % )

◇ Total PLLs : 52 / 80 ( 65 % )

◇ DDR

- 使用メモリ :4Gb(256Mx16 MT40A256M16GE-083E)×4

- メモリクロック :933.33MHz

上記の値は、弊社実装例に基づく回路規模の概算値および使用デバイスです。お客様のシステム構成により変動する場合があります。

ブロック図

リリース状況 / スケジュール

◇ 販売中

提供物

★ハードウェアIP

○ Quartus®用暗号化RTL

○ Questa Sim用暗号化シミュレーションモデル

○ Quartus用ライセンスファイル

★ソフトウェア開発キット

○ SDKソフトウェア (Software Suite、Library Suite)

○ ST2059 Library

○ NMOSアダプタソフトウェア (オプショナルコンポーネント) ※計画中

★ドキュメント

○ ユーザーズマニュアル

★リファレンスデザイン

○ ハードウェア: Verilog記述によるリファレンスデザイン

○ ソフトウェア: デバイスドライバ、リファレンスアプリケーション

*リファレンスデザインについては、“AS-IS”かつ“非保証”での提供となります