IPネットワーク伝送・時刻同期をサポート

概要

IEEE 1588v2 Precision Time Protocol(PTP)を使用してSMPTE® ST2059で定められたTiming信号を生成し、IPベースのA/V伝送で従来使用していたGenLock信号として運用できます。

特長

- IEEE 1588v2 Master/Slave mode対応

- FPGAのHWと組み合わせることにより、より柔軟にカスタマイズ可能

- より強いNetwork Jitter耐性

- 短縮されたLock時間

仕様

- IPv4 Base

- Master/Slave両対応

- Video/Audio AP output

- 1pps output

- TC output

対応デバイス

- Cyclone V SX

- Arria 10 SX

(※その他のデバイスの対応状況については、弊社営業までお問い合わせください)

提供物

- バイナリー SW

- 暗号化RTL(Verilog HDL)

- リファレンスデザイン

- 各種マニュアル

ロジックリソース

弊社営業までお問い合わせください。

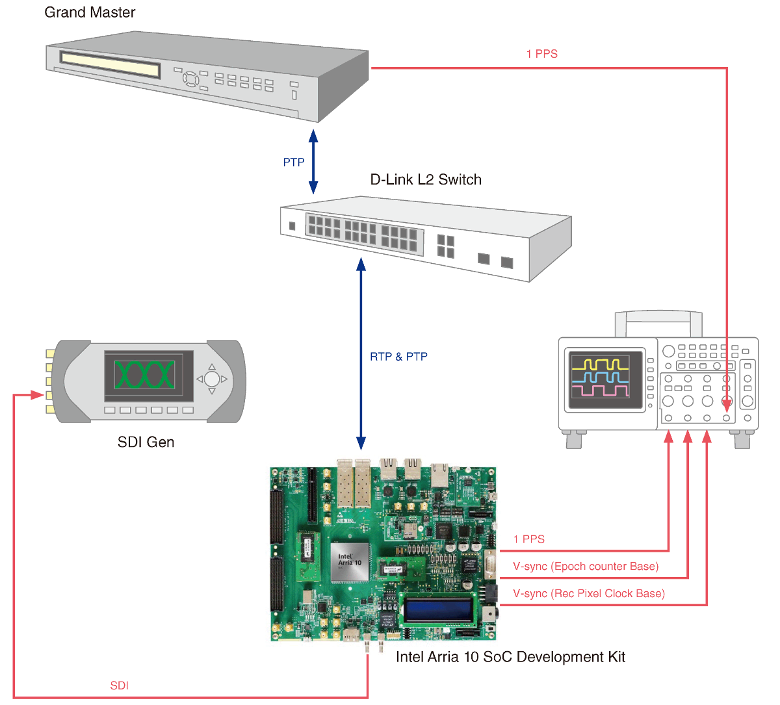

デモイメージ