ソニーによる次世代CMOSイメージセンサーのインターフェースをFPGAで実現

概要

SLVS-EC Rx IPは、Intel® FPGAでSLVS-ECの受信を実現させるためのIPです。SLVS-ECは、ソニーが提唱する、高解像度CMOSイメージセンサー向け高速シリアルインターフェースの規格です。

この規格は、ピクセルデータにクロックを埋め込んだEmbedded Clockを採用しており、レーン間で発生するSkewを意識することなく基板設計を行うことができます。そのため、高速化や長距離伝送に有利となっています。

特長

- SLVS-EC Specification Version 1.2/2.0対応

- SLVS-EC Link層で定義される各種機能を実現(物理層はIntel® PCS/PMAで実現)

- 各種レーン構成におけるByte to Pixel変換をサポート

- ヘッダー解析とペイロードエラー検出機能を搭載

仕様

| 機 能 | 諸 元 |

| Number of Lanes | 1、2、4、6、8 |

| Baud Grade | 1、2、3※ |

| Bit per Pixel | 8、10、12、14、16 |

| CRC | Limited※ |

| ECC | Option 1 |

| Embedded Data | Supported |

| Dynamic Mode Change | Supported |

| Multiple Stream | If needed |

※ Baud Grade 3は、10シリーズ以降のみサポート

※ CRCは、使用するFPGAのSpeed GradeとLane数等の構成により動作周波数を満たせない場合があります。

※ IPの非サポート機能や制限事項については、弊社営業までお問い合わせください。

対応デバイス

- Cyclone® V GX

- Cyclone® 10 GX

- Arria® 10 GX

- Stratix® 10 (L-Tile/H-Tile)

(※その他のデバイスの対応状況については、弊社営業までお問い合わせください)

提供物

- 暗号化RTL(Verilog HDL)

- リファレンスデザイン

- シミュレーション環境(Modelsim用)

- ユーザーズマニュアル、リファレンスマニュアル、シミュレーションマニュアル

ロジックリソース

8レーン構成でTransceiverを含んだ回路構成となります。

| Items | Cyclone® V GX | Arria® 10 GX | ||

| w/o ECC | w/ECC | w/o ECC | w/ECC | |

| ALMs | 4711 | 8242 | 3930 | 7555 |

| Total Registers | 4328 | 6664 | 3778 | 6079 |

| Total block memory bits | 4096 | 13312 | 2560 | 11776 |

※ 上記の値は8LaneのFull ConfigurableおよびIP+Transceiverの合算での回路規模の概算値です。お客様のシステム構成により変動する場合があります。

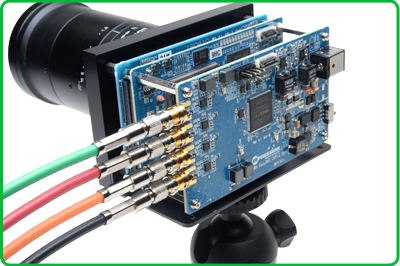

評価・デモ環境

このIPは、弊社のEasyMVCマシンビジョンカメラ開発キットを使用して、評価やデモが可能です。