V-by-One® HS規格による高速シリアル伝送を実現

概要

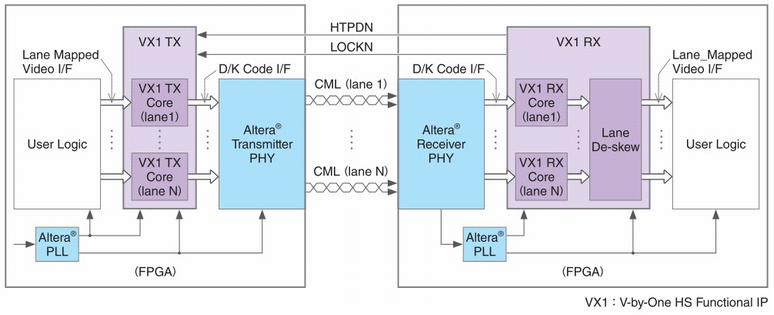

V-by-One® HS Tx/Rx IPは、V-by-One HS高速インターフェースを実現するためのIPです。

V-by-One® HSとは、ザインエレクトロニクス社が画像・映像機器向けに提唱する次世代の高速インターフェース規格です。

Mpressionが提供するV-by-One® HS Tx/Rx IPをインテル®FPGAに実装すると、従来のLVDSインターフェースに比べ信号本数を減らせるため、製品コストの大幅な削減につながります。

特長

- 1レーンあたりの最大伝送帯域は4Gbpsを実現(ただし、適用するFPGAに依存)

- VESA/SMPTEなどで規定された映像フォーマットだけでなく、ユーザーカスタムの映像フォーマットにも対応

- お客様の伝送帯域に合わせた柔軟なマルチレーン設計が可能

- 送受信IP間で通信確認を行うためのセルフチェック機能(FieldBET機能)を搭載

仕様

| Transmitter IP (TX) | Receiver IP (RX) | |

| Lane | 1-32 | |

| Pixel Data | 24, 32,40 bit | |

| Seif Test Function | FieldBET Pattern Generator | FieldBET Pattem Checker |

対応デバイス

- アルテラ® Agilex™ 5E(Group B)

- アルテラ® Agilex™ 7(F Tile)

- アルテラ® Stratix® 10 GX( H/L Tile )

- アルテラ® Arria® 10 GX

- アルテラ® Cyclone® 10 GX

※アルテラ Stratix® V GX, Arria® V GX, Cyclone® V GX ファミリーについては弊社までお問い合わせください。

提供物

- 暗号化RTL(Verilog HDL)

- リファレンスデザイン

- シミュレーション環境(Modelsim用)

- ユーザーズマニュアル

- リファレンスデザインユーザーズガイド

ロジックリソース (アルテラ® Arria® 10 GXの場合)

RX

| 2Lane | 4Lane | 8Lane | 32Lane | |

| ALMs | 2,419 | 4,640 | 9,262 | 37,265 |

| registers | 4,977 | 9,956 | 19,914 | 79,309 |

TX

| 2Lane | 4Lane | 8Lane | 32Lane | |

| ALMs | 1,531 | 3,067 | 6,709 | 24,542 |

| registers | 2,814 | 5,567 | 11,276 | 45,076 |

構成図

評価ボード