はじめに

本記事は、スカイワークス社のサイト上で公開されているブログ記事の日本語訳版になります。

クロックに関する技術記事が多数存在する中、第二弾として"Analog PLL (APLL) vs Digital PLL (DPLL)の構造の違い"について触れています。

ご興味があれば、オリジナルのスカイワークス社ブログ記事もぜひご一読ください。

スカイワークス社 技術ブログ記事「Timing Timing 201 #7: The Case of the Dueling PLLs - Part1」

※第一弾「複数クロックIC接続時のトータルジッタ算出方法とは?」に関してはこちらから。

従来のPLL構成とスカイワークスのDSPLL技術

RFおよびマイクロ波周波数シンセサイザは、多くの場合、複数直列接続(カスケード接続)されたAnalog PLL (APLL)を採用しています。

この構造の場合は、位相ノイズの改善、周波数ステップサイズの縮小、およびスイッチングの高速化を得られる一方で、複雑さが増すため、トレードオフの関係にあります。

複数のPLLを接続・使用する目的は様々ですが、例えば

・PLL1:各PLLを使って異なる基準周波数から任意の出力周波数を生成。

・PLL2:複数の基準信号に対して、切替時にスムーズな同期ループを確保。

・PLL3:外部からのクロック信号に含まれるジッタを除去し、綺麗なクロックを生成。

その他:低位相雑音の実現

特定のPLLを低雑音設計とし、他のPLLの出力を基準信号として利用することで、システム全体の位相雑音を低減、

またPLL間で位相雑音を分離し、特定の動作周波数帯域での雑音を最小化するなどが挙げられます。

スカイワークス社は、直列接続されたAnalog PLL (APLL)とは対照的に、

一つのPLLに集約、二重ループ構造をもったDSPLLという彼ら独自の技術を詰め込んだPLLを採用しています。

ホワイトペーパー「Optimizing Clock Synthesis in Small Cells and Heterogeneous Networks」では、

スモールセル・アプリケーション向けのジッタクリーナ(Si538x)で使用されている、DSPLLについて説明しています。

直列接続されたAnalog PLL (APLL)

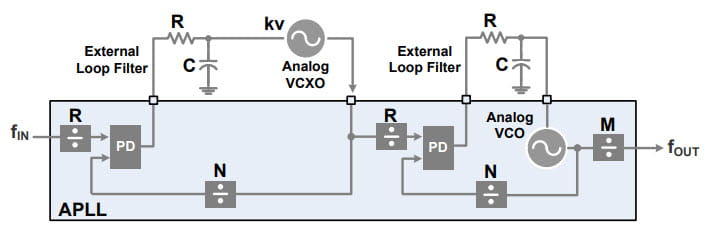

下の図は、直列接続されたAnalog PLL (APLL)を示しています。

カスケードという用語は、ここでは2つのPLLを連結または直列に接続することを意味しています。

2つのPLLを直列に接続することで、ジッタ除去と周波数合成を組み合わせたシステムを実現できます。

図の左側のPLLと右側のPLLをそれぞれ、PLL1(左側)/PLL2(右側)とします。

・PLL1

・VCXO(アナログ電圧制御発振器)を使用。

・狭帯域のジッタ減衰器として機能。

・出力クロックのジッタを減衰し、綺麗なクロック信号をPLL2にパス。

・PLL2

・広帯域のクロック生成として機能。

・PLL1の出力クロックを受け取り、所望の出力クロック周波数を生成。

図のようなPLL設計かつ外付けにアナログ電圧制御発振器(VCXO)やループ・フィルタを必要とするため、Analog PLL (APLL)に分類されます。

二重ループ構造となるDigital PLL (DSPLL)

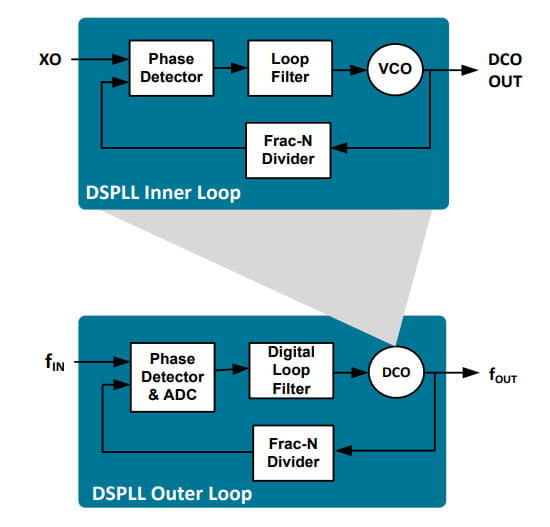

下の図は、一つのPLLに集約された二重ループ構造のDigital PLL (DSPLL)を示しています。

インナー・ループ(IL)とアウター・ループ(OL)の2つのPLLを組み合わせた二重ループ構造です。

・アウター・ループ(OL)

・デジタル・ループ・フィルタを含有。

・インナー・ループ(IL)の動作を制御する役割。

・インナー・ループ(IL)

・アウター・ループにとってのVCO(電圧制御発振器)として機能。

・実際には、VCOの代わりにDCO(デジタル制御発振器)を使用。

このように一つのループの中にもう一つのループが入っており、二重ループ構造となっています。

動作の仕組みとしては、アウター・ループ(OL)のデジタル・ループ・フィルタの出力がインナー・ループ(IL)のリターン・パスを変調(調整)します。

つまり、インナー・ループ(IL)の動作がアウター・ループ(OL)によって制御されます。

最終的に、インナー・ループ(IL)のVCO(DCO)からクロック信号(fout)が出力されます。

※実際のシステムでは、このfoutをさらに分周して、必要な出力クロックを生成します。

インナー・ループ(IL)とアウター・ループ(OL)によって調整されるため、位相ノイズ性能の最適化が可能となっています。

このように、一つのPLLに集約された二重ループ構造のDigital PLL (DSPLL)は、より高精度な周波数合成や低位相ノイズ設計に活用されます。

そして、ループ・フィルタやVCOの一部はデジタル回路で構成され、プログラム可能な特性を持つことからDigital PLL (DPLL)に分類されます。

APLLの課題とDSPLLの利点

直列接続された Analog PLL (APLL)の課題としては、

VCXOはICに外付けされるため、外部制御電圧が必要かつ 近接位相雑音(低周波数オフセットのノイズ)も良好である必要があります。

内部VCOは十分に高い周波数で動作する必要があるほか、高いオフセット周波数でも低位相雑音である必要があります。

このように、外付けには性能の良いVCXOやフィルタなどの要素が必要となり、部品選び、定数決め、外付け分のコストアップ、面積拡大などが課題として挙げれられます。

二重ループ構造となるDigital PLL (DSPLL)の利点としては、

外付けのVCXOやループ・フィルタは不要で、それらは内部にネスト(入れ子)として集約され、かつデジタル制御により最適化されています。

そして部品が減る事による、コスト減、実装面積縮小が得られるほか、設計工数も削減することができます。

DSPLLの注意点

二重ループ構造となるDigital PLL (DSPLL)のフィードバック制御ループでは、内側のループは外側のループよりも速くなければなりません。

もしループ速度が同等であれば、ループは互いに干渉し合い、安定性を損なう可能性があります。

速いPLLと遅いDCOを組み合わせるとPLLの応答が速すぎてDCOが追従できず、ループに遅延が生じます。

遅いPLLと速いDCOを組み合わせるとPLLの応答が遅いため、DCOが速くても大きな影響を与えることなく、問題が発生しにくいです。

このため、設計上「内側のループは広帯域(速い)」、「外側のループは狭帯域(遅い)」とするのが望ましいです。

また、システムを安定させるためには、内側のループを先にロックさせるべきです。

外側のループは、内側のループがロックしている前提で動作するため、順番が逆だと不安定になります。

まとめ

直列接続された Analog PLL (APLL)は、従来からある構成ですが、VCXOやループフィルタ回路等の外付け部品の影響が大きいです。

一方、二重ループ構造となる Digital PLL (DSPLL)では、同様の要素機能をPLL内に内蔵しているので、一般的なAnalog PLL (APLL)構造と比較して設計の自由度が上がり、BOMコストや実装面積でメリットがあります。

スカイワークス社のクロックICは、彼ら独自のDSPLL技術を採用し、低ジッタ・高精度なクロック生成を実現しています。

関連記事

DSPLL搭載、低ジッターなスカイワークス社、クロックICにご興味あれば、以下の記事もぜひ、ご一読ください。

【DL資料あり】SKYWORKS社 タイミング製品・全体ラインナップ資料のご案内

インテル社FPGA開発キットに低ジッタ・タイミング製品多数搭載!~スカイワークス社の豊富なリファレンスデザイン/クロック情報のご案内~

スカイワークス社メーカ情報Topへ

スカイワークス社のメーカー情報Topページに戻りたい方は以下をクリックください。