はじめに

本記事は、スカイワークス社のサイト上で公開されているブログ記事の日本語訳版になります。

クロックに関する技術記事が多数存在する中、第一弾として"クロックツリーとジッター算出方法"について触れています。

ご興味があれば、オリジナルのスカイワークス社ブログ記事もぜひご一読ください。

スカイワークス社 技術ブログ記事「Timing Timing 101 #11: The Case of the Noisy Source Clock Tree Part 1」

クロックツリーとは?

クロックには切っても切れないジッターという、信号品質に影響を与える存在がいます。

そして、一つの系にクロックICが複数あり、出力するクロック本数も多い場合は、ジッターがどのように表れ、またクロック信号に影響を及ぼすのかイメージすることは難しいです。

リファレンスクロックのジッターを低減させるクロックICとしてジッタークリーナー(ジッターアッテネーターとも呼ぶ)がありますが、

ジッタークリーナーが必要な場合とそもそものジッターの算出方法について本記事でご紹介します。

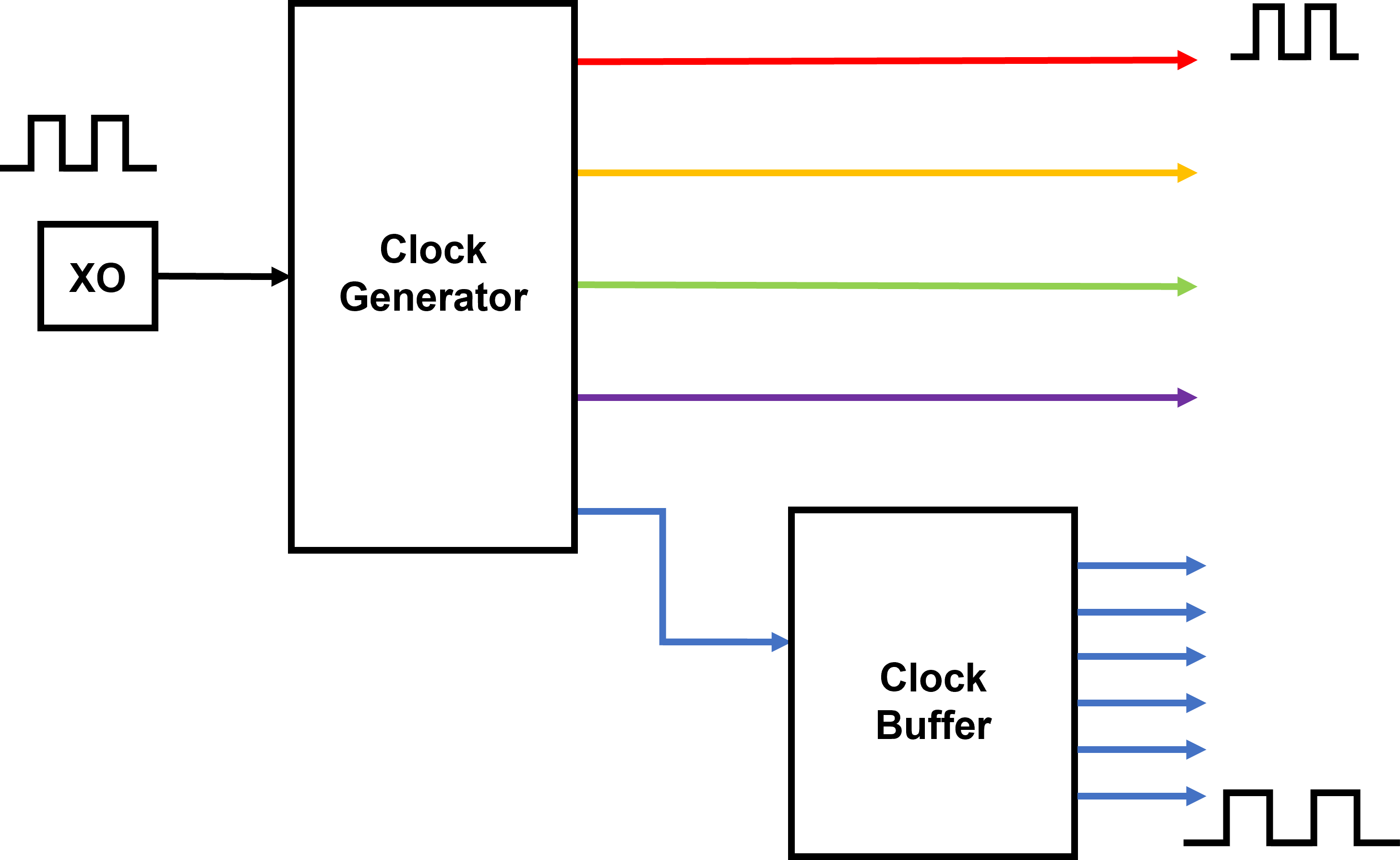

データセンターや通信基地局、システム内でクロックを複数分配する必要があるアプリケーションなどは、

通常、クロックジェネレーターに接続された水晶振動子または低ジッターXO(水晶発振器)と、それに続く1つまたは複数のバッファーで構成されます。

このような一連のつながりを持ったクロックデバイス構成をクロックツリーと呼んでいます。

次の図は、クロックツリーの構成例です。

クロックツリーから総ジッター量を算出

この例では、クロックツリー全体の周波数安定度を決定する低ジッターXOがクロックのソースとなっています。

次にクロック・ジェネレーターは、そのXOからの入力周波数をもとに複数の異なる出力周波数を生成します。

最後に、クロック・バッファーがこれらの出力周波数の1つを取り込み、同じ周波数を持つ複数の出力クロックを分配(複製)します。

※図中の色の付いた矢印は、異なるクロック周波数を示しています。

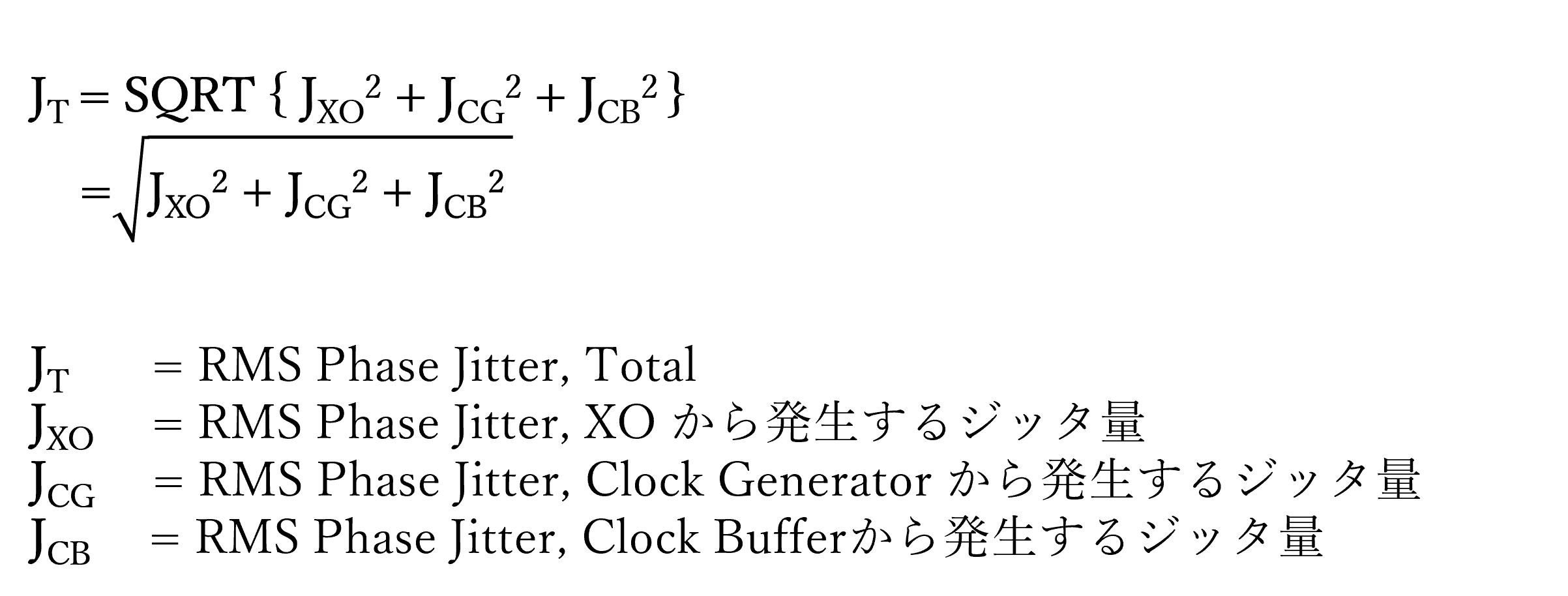

クロックツリーのエンドのクロックが持つジッターはそれぞれのクロックICのジッター成分を足せば、求められそうに思いますが、単純な足し算では求まりません。

それぞれのクロックが持つジッター成分を時間領域ではなく周波数領域で解析することがジッターの評価には有効です。

各クロックICがもつ位相ノイズを各オフセット周波数で測定し、特定の帯域(12kHz~20MHzなど)で、それら位相ノイズを積分します。

積分した結果はRMSジッターとして表され、

2乗和の平方根を用いる事で、クロックツリーのエンドのクロックが持つトータルのジッターを推定することができます。

上記の例では、RMS位相ジッターの合計を次のように見積もることができます。

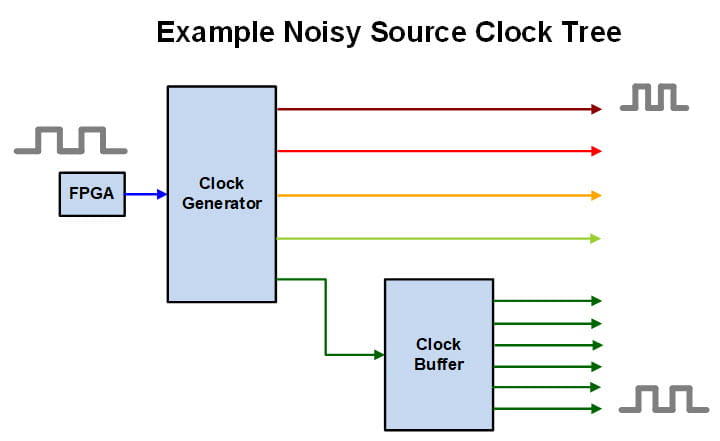

ノイズを持ったクロックソースの例

クロックツリーの例では、クロックのソースが低ノイズであることを前提としていますが、すべてのクロックツリーがそうとは限りません。

実際は、シリアルデータから再生成されたものや、FPGAから作られたものかもしれません。

また、基板自体がXOに電源ノイズを与えている場合もあります。

そんな場合、クロックツリーは下図のように動作し、ジッターが大きくなります。図ではそのことを示すために波形が前の図より太く描かれています。

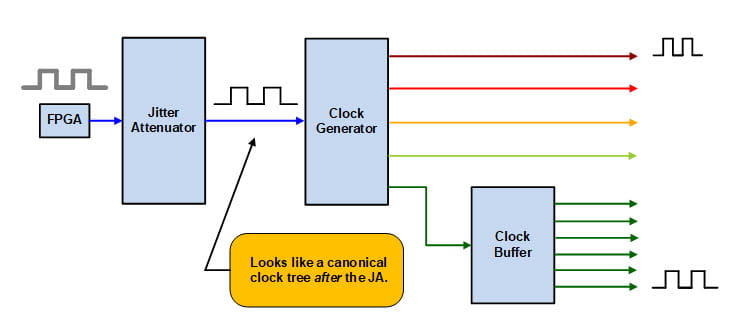

ジッタークリーナーによるジッター低減!

ノイズ多いクロックツリーを改善するためには、ジッタ―クリーナーを使ってソースクロックのノイズを取り除き、クロックツリー全体のジッター性能を良くする必要があります。

下の図では、ノイズの多いFPGA由来のソースクロックとクロックジェネレーターの間にジッタークリーナーを挿入して、クロックをきれいにする仕組みを取り入れています。

ジッタークリーナーを通した後のクロックツリーは、前の図とは異なり、ノイズが少ないクロックツリーと同じように動作します。

実際のクロックICでは、ジッター低減に限らず、周波数設定も可能で、ジッタ―クリーナ―とクロックジェネレーターの役割を一つのデバイスが兼ねることもよくあります。

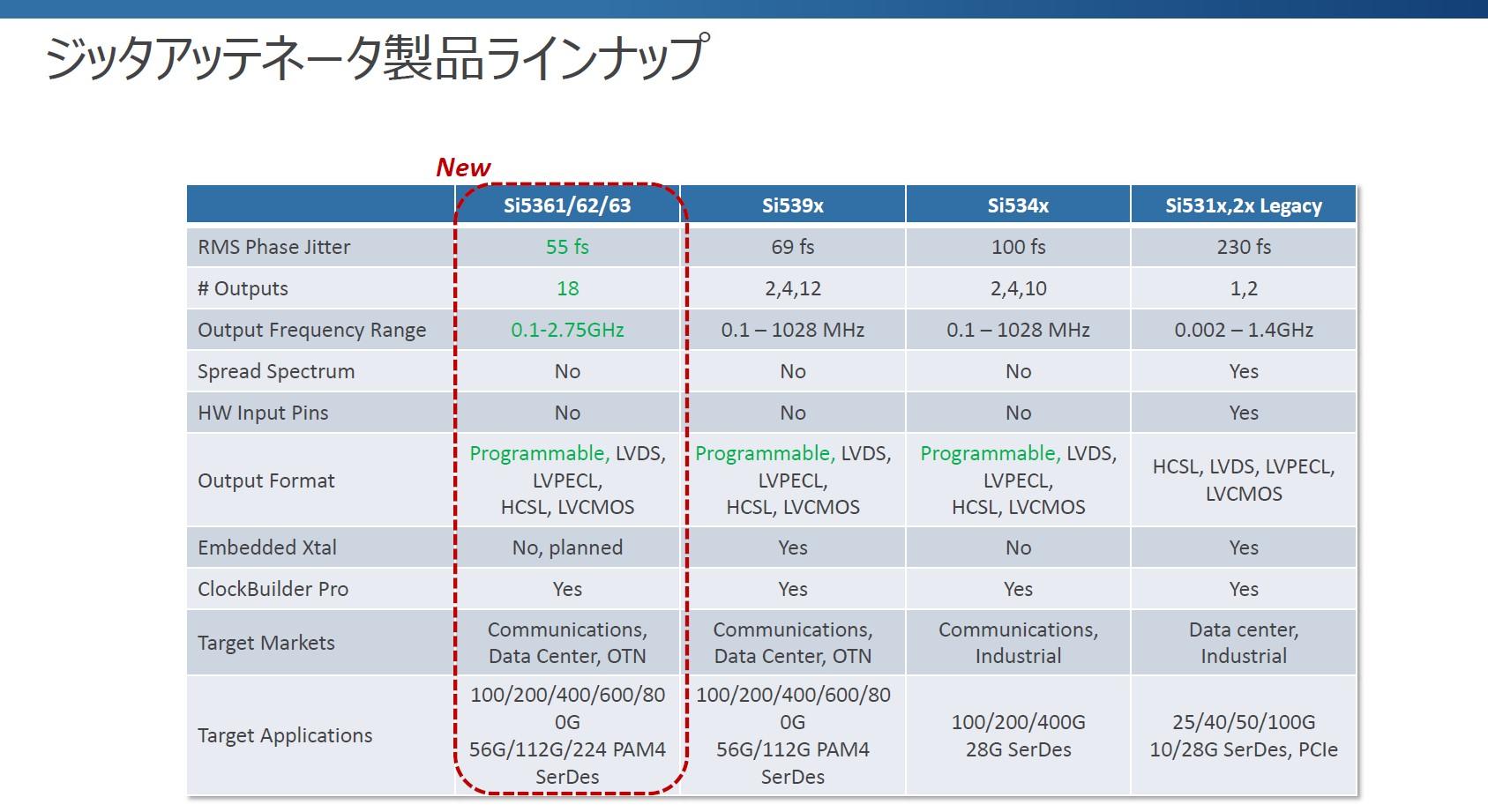

スカイワークス社 ジッタークリーナーのラインナップ

スカイワークス社のジッタ―クリーナーは、低ジッター性能で、ノイズの多いクロックソースからも低ジッターで高精度なクロック信号を生成します。

スカイワークス社、独自のDSPLL(位相ロックループ)技術を採用し、低ジッターで非常に細かい出力周波数設定を実現でき、クロックツリー全体のジッターを最小限に抑えます。

これにより、データセンター、通信インフラ、工業用機器など、厳しいタイミング要件を求められるアプリケーションでも安定した動作をサポートします。

スカイワークス社、ジッタークリーナーのラインナップは以下になります。

まとめ

ジッターの計算方法は、その種類に応じて異なりますが、一般的には、周波数領域での解析が位相ジッターの評価には有効です。

RMS位相ジッタ―は各オフセット周波数における位相ノイズから計算され、クロック信号におけるジッターの周波数成分を解析し、低周波成分の影響と高周波成分の影響を分離して理解するために重要です。

クロックソースをはじめに、クロックジェネレーター、バッファーを通ることで、どれほどのジッターが発生するのかを把握し、ジッタークリーナーを使用することで、

最終的な出力の結果が、要求されるジッター性能を満たしているのかを確認することが重要です。

以上、本記事がお役に立てれば幸いです。

関連記事

低ジッターなスカイワークス社、クロックICにご興味あれば、以下の記事もぜひ、ご一読ください。

【DL資料あり】SKYWORKS社 タイミング製品・全体ラインナップ資料のご案内

インテル社FPGA開発キットに低ジッタ・タイミング製品多数搭載!~スカイワークス社の豊富なリファレンスデザイン/クロック情報のご案内~

スカイワークス社メーカ情報Topへ

スカイワークス社のメーカー情報Topページに戻りたい方は以下をクリックください。