回路設計の現場では、製品小型化要求のために基板上の部品実装面積が制限される場合や、トータルBOMコスト低減を目的に複数部品の集約化などが求められます。ルネサスエレクトロニクス社(以下ルネサス社)のGreenPAKを用いることで、そのような要求に対応することが出来ます。本記事では、GreenPAKがどのように活用されているのか、実際の回路設計現場の事例を取り上げてご紹介します。

GreenPAKとは

ルネサス社のGreenPAKとは、超小型のデジアナ混載プログラマブルICです。複数のIC・ディスクリート部品の機能を1チップに集約し、カスタム仕様の作り込みが可能です。ロジックICを始め、ADC/DAC、クロック、コンパレーター、それらに付随するディスクリート部品と同様の機能をGreenPAKに実装することが可能です。

カスタム仕様の作り込みにあたっては、Go Configure™ Software Hub(無償ツール)を使用します。

電源システム小型化の課題

今回、実際の開発現場であった事例をご紹介して、こちらを元に実装を進めたいと思います。

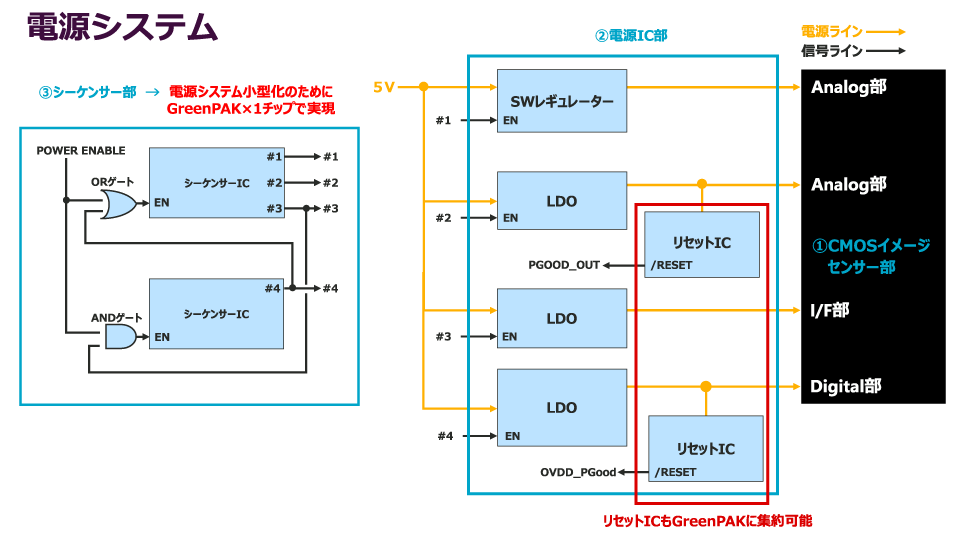

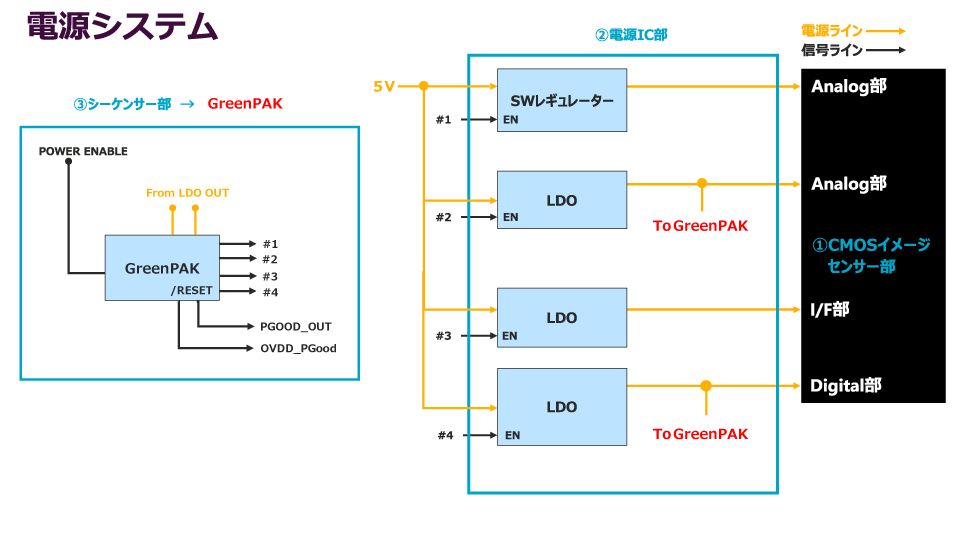

検討中の電源システムは図1のようになっていました。

図1の通り、電源システムの構成は大きく分けて3つです。

①CMOSイメージセンサー部

②電源IC部(CMOSイメージセンサーに電源を供給)

③シーケンサー部(各電源ICのON/OFFを制御)

電源システムを検討する上で、

「基板上のIC実装スペースに余裕がないため、電源システム構成をシンプルにしたい」

という課題がありました。

そこで、シーケンサー部をGreenPAK×1チップで実現することで、上記課題を解決できないか検討を開始しました。

GreenPAKによる電源シーケンサー実装手順

GreenPAKに実装する回路

今回の電源システムにおける、シーケンサー部の要求仕様と構成は以下のようになっています。

【シーケンサー部の要求仕様】

・4つの電源IC(SWレギュレーター×1、LDO×3)のON/OFFを制御できること

・各電源ICのONシーケンスの順番は、#1→#2→#3→#4

・各電源ICのOFFシーケンスの順番は、#4→#3→#2→#1

・ON/OFFシーケンスは、それぞれ200ms以内に行う

・シーケンサー電源は5V

【シーケンサー部の構成】

先ほどのシステム図の通り以下構成になっています。

・シーケンサーIC × 2

・ORゲートロジック × 1

・ANDゲートロジック × 1

【シーケンサー部の構成】をGreenPAK×1に置き換えて、同時に【シーケンサー部の要求仕様】を実現させます。

また、電源IC部のリセットIC×2もGreenPAKに集約可能です。

GreenPAKで電源シーケンサー回路を作成

まずはGreenPAKの回路作成ツール:Go Configure™ Software Hubを開きます。

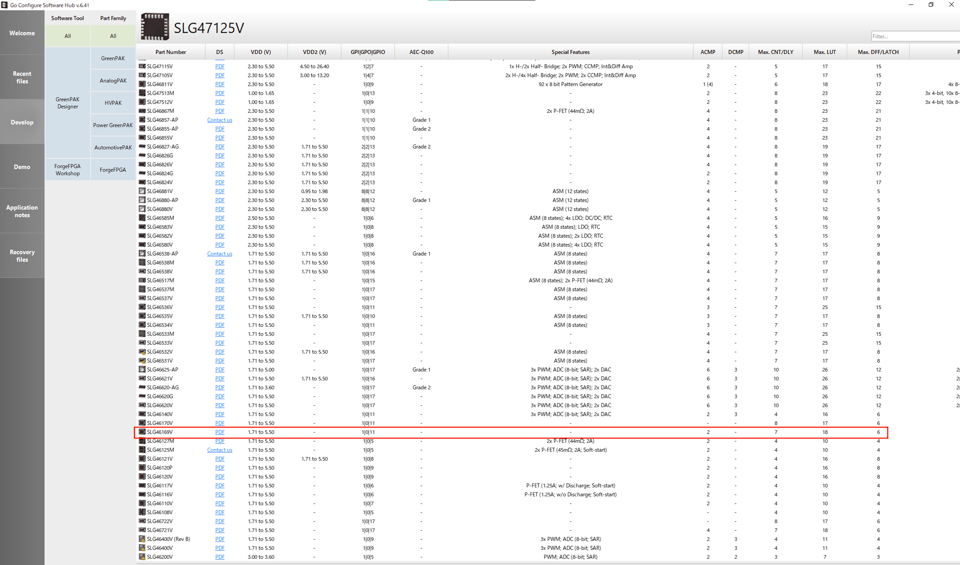

図3の型番指定画面で、今回の仕様を実現できるようなリソースを有したGreenPAK型番を指定します。今回は4出力電源シーケンサー×1とリセットIC×2をGreenPAKに実装します。必要I/O数、CNT/DLY数、ACMP数などを考慮し、SLG46169Vに決定しました。

CNT/DLY:遅延回路に必要

ACMP:リセットICの電圧検出に必要

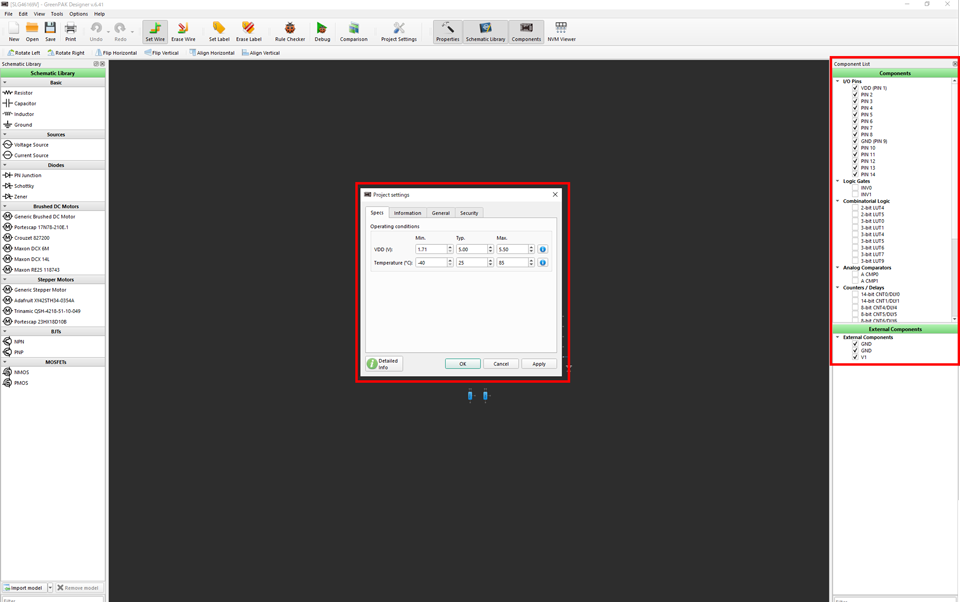

図4で、型番をダブルクリックするとGo Configureの開発画面が開きます。真ん中のウィンドウでデバイスの電源電圧範囲を指定します。今回はTyp.5.0Vに指定します。

次に、実際に回路を作成していきます。画面右側の”Components”ウィンドウから、使用するマクロセルにチェックを入れ、画面中央のWork Areaに各マクロセルを出現させます。

【今回使用するセル】

■電源シーケンサー部

・I/O PIN ×5

・3-bit LUT ×4

・CNT/DLY ×4

・OSC(内臓オシレーター)×1

■リセット回路部

・I/O PIN ×4

・2-bit LUT ×2

・CNT/DLY ×2

・ACMP(アナログコンパレーター)×2

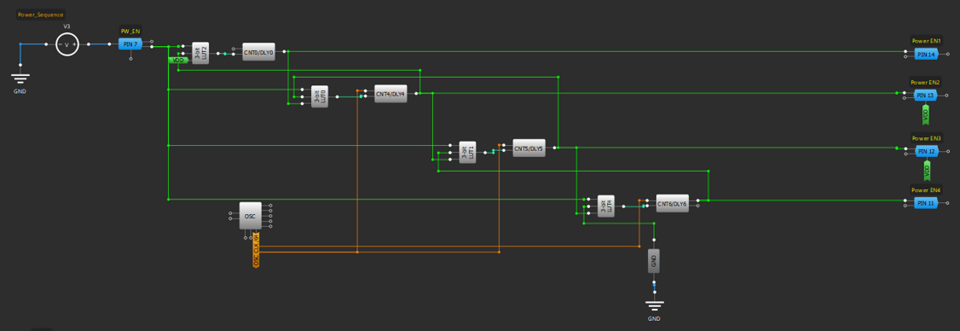

マクロセルを配置できたら、電源シーケンサー回路を作成します。リセット回路の作成手順については、GreenPAKでリセットICを作ってみた に詳しく載っていますのでこちらをご確認いただけたらと思います。電源シーケンサー回路を構成するために、各マクロセルを図5のように結線しました。

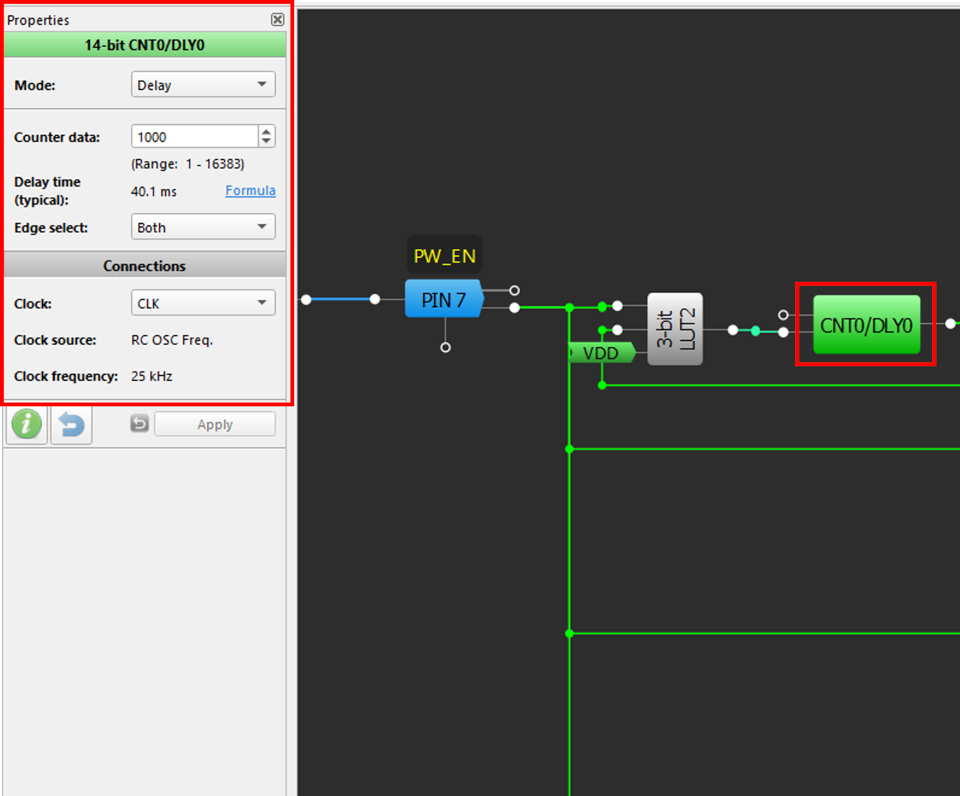

遅延を作り出すCNT/DLYセルをダブルクリックすると、画面左側にPropertiesウィンドウが表示されます。基準Clockはデフォルト設定のままとし、Counter dataの値を任意の値に設定することで、Delay timeを決定します。今回は、4つの電源ICを200ms以内に立ち上げなければならないので、CNT/DLYセル1つあたりのDelay timeを約40msとなるよう、Counter dataの値を設定します(全てのCNT/DLYセルに同様の設定をおこなう)。

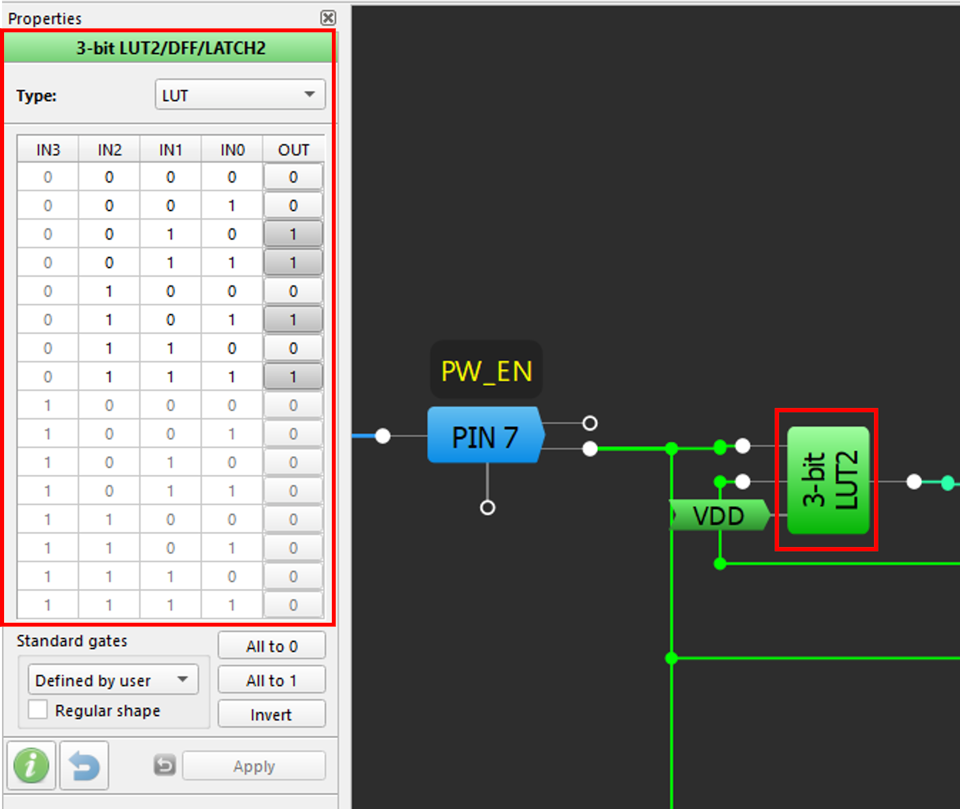

次に、立上げ・立下げシーケンスのロジックを作るため、3-bit LUTセルをダブルクリックします。画面左側のPropertiesウィンドウに真理値表が表示されますので、図7のように、出力値を設定します(全ての3-bit LUTセルに同様の設定をおこなう)。

ここまでで、回路作成とマクロセルの設定は完了です。

〇シミュレーション確認

Go Configure上のシミュレーションソフトで、今回作成した電源シーケンサー回路が期待の動作をおこなうかどうか確認します。

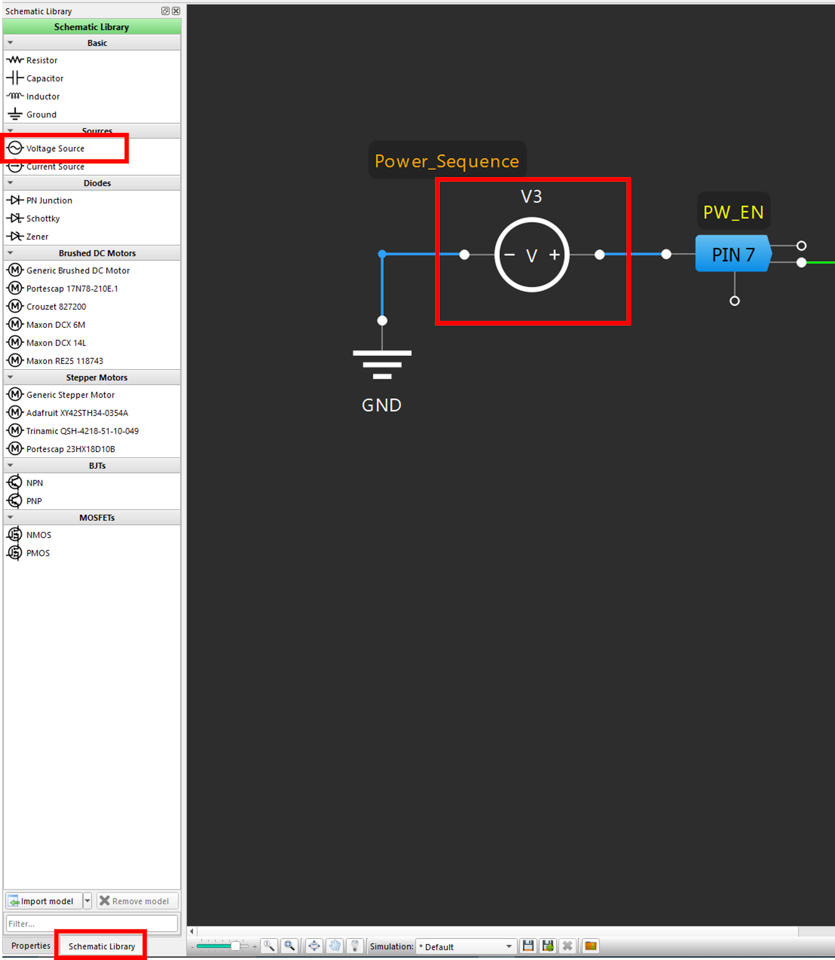

左側のウィンドウ画面下部で、”Schematic Library”のタブを選択すると、ウィンドウが切り替わりますので、ウィンドウ内に存在する ”Voltage Source”をクリックしWork Areaに配置します。図8のように+側を入力ポートに、-側をGNDに結線をおこないます。

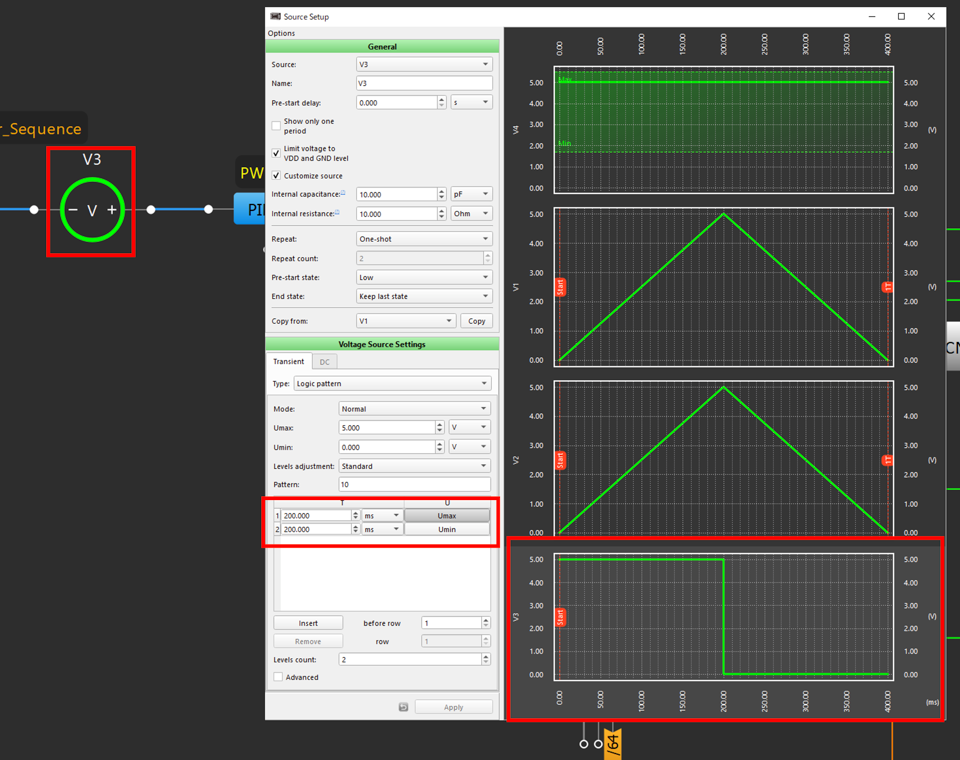

Voltage Sourceのシンボルをダブルクリックすると、信号設定画面が出てきます。ここで、入力したい波形を設定します。今回の電源シーケンサーは、Enable信号を入力信号として受けます。

HiレベルのEnable信号入力後、所定のONシーケンスがおこなわれ、LoレベルのDisable信号入力後、所定のOFFシーケンスがおこなわれることを確認できるよう、図9のようにHi:200ms、Lo:200msの入力波形を設定します。

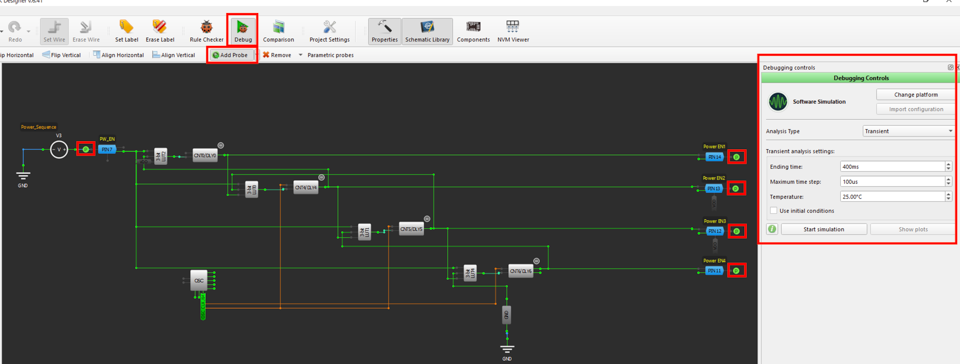

シミュレーションをスタートさせるために、画面上部の”Debug”をクリックし、“Add Probe”が選択された状態で、波形を測定したい箇所にプローブシンボルを配置します。

次に、右側ウィンドウにて、Ending timeを400ms、Maximum time stepを100μsに設定し、“Start simulation”をクリックします。

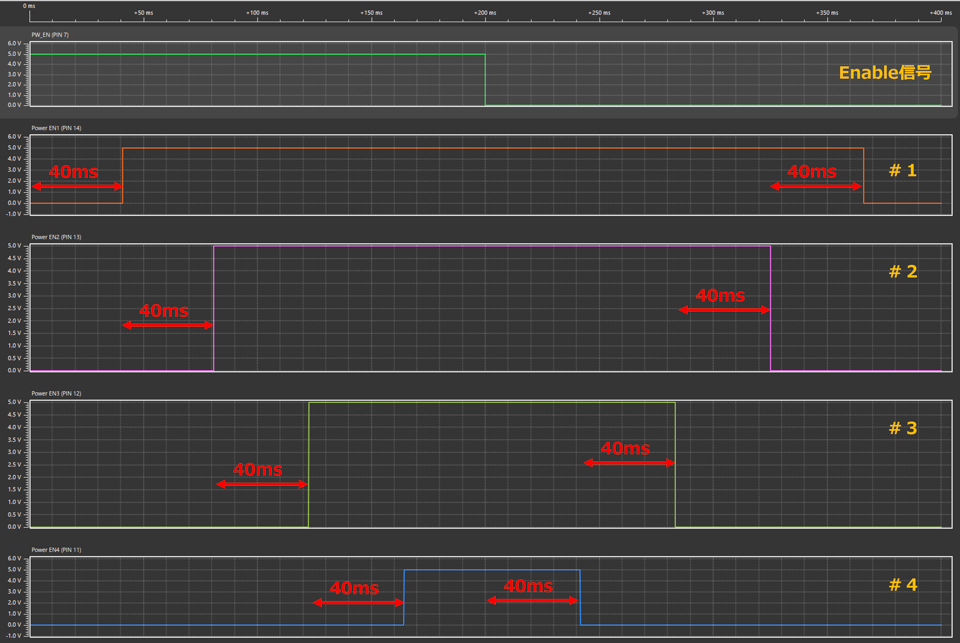

シミュレーション波形が以下です。

HiレベルのEnable信号を受けて、4本の信号それぞれが約40msずつ遅れて、#1→#2→#3→#4の順番で立ち上がっていることが確認できます。

Enable信号がLoレベルに落ちると、4本の信号それぞれが約40msずつ遅れて、#4→#3→#2→#1の順番で立ち下がっていることが確認できます。

まとめ

実際の開発現場の事例を取り上げてGreenPAKによる電源シーケンサー回路の作成手順をご紹介しました。今回は複数ICを1チップに集約し、外付けコンデンサーを使用せずに柔軟に遅延量を設定、ソフトウェア上でシミュレーションをおこなうことで回路の妥当性を確認できました。GUIの操作も直感的に分かりやすくなっておりますので、ぜひ本製品をご活用ください。