フライバックコンバーターの損失を画期的に改善するためのSiC半導体

190億ドルをどうしますか?天然資源防衛評議会によると、これは2015年に米国市民が「待機状態」にあるだけの機器や電化製品の電気代として支払った金額です。あなたの取り分は約60ドルにしかなりませんが、環境コストを考えると、50基の大規模発電所の運転に相当します。許容可能な待機損失は通常0.5W未満ですが、「5つ星」評価のためには30mW未満である必要があります。

物差しのもう一方の端では、省エネのためだけでなく、小型化による熱放散量の減少という付加的なメリットのために、デバイスや電化製品の全負荷損失を低くする必要があります。これは、電力変換段階での高い変換効率を意味します。これに低コスト化への執拗な圧力が加わり、AC/DCコンバーターの設計者は厳しい課題に直面しています。

ワイド・バンドギャップ(WBG)半導体を使用したハイパワー・コンバーターの最新技術は、90%以上の効率を実現しており、スタンバイ時には主コンバーターを完全に無効にし、小型の補助コンバーターを動作させたままにして、デバイスを素早く起動できるようにしておくことが、低損失化のための効果的なソリューションです。

これは、低電力コンバーター、典型的にはフライバックが、携帯電話の充電器や小型機器のような主電源である場合の損失と同様に、大型機器のスタンバイ時の損失を定義することを意味します。低電力AC/DCの効率を最大化しようとすると、すべてのミリワットの損失がカウントされ、制御ICに電力を供給する回路が重要な貢献者となります。最初に、起動時の電流はAC電源から供給されなければならないため、高電圧、高出力の電力用抵抗、または直列に複数の抵抗器を使用して、電圧をクランプするために、ICに内蔵されていることが多いツェナーダイオードを使用することがあります。低ACラインでは十分な起動電流が得られるように抵抗器のサイズを調整する必要がありますが、高ラインでは抵抗器にかかる電圧が3倍になり、3倍の電流とツェナーでの損失で9倍の損失が発生します。

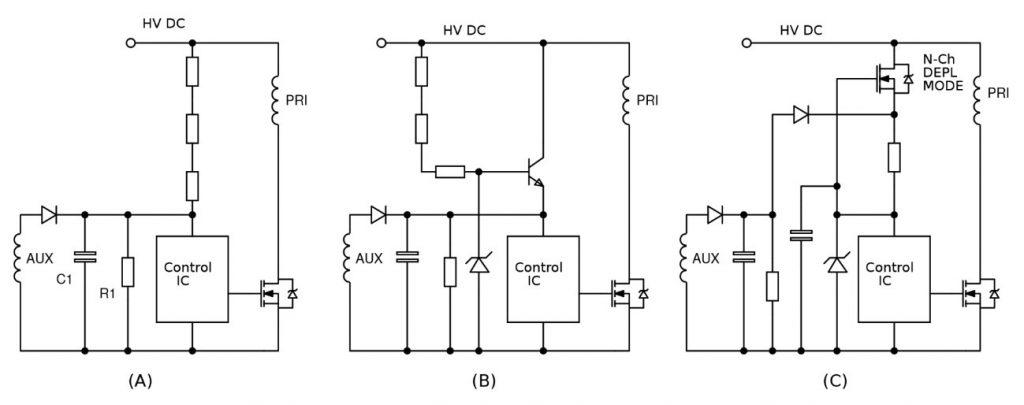

最悪の場合、ワット単位の電力が失われることがすぐにわかります。そのため、解決策は、抵抗を非常に高い値にしてコンデンサーを充電し、ICの低電圧ロックアウトに達したときに十分な起動エネルギーを放出することです。その後、補助電源が引き継ぎます(図1A)。すべての動作条件下で補助電源がツェナー電圧を超えるのを防ぐために、補助電源にはプリロード(R1)が必要な場合があります。消費を最小限に抑えるには、抵抗とコンデンサーの両方を非常に高い値にする必要がありますが、起動時間は数秒で許容できない場合があります。

直列トランジスタ(図1B)は、ICのツェナーからの消費を移動するのに役立ちますが、問題を移動しているだけです。コンバーターが補助電源の使用を開始した後にトランジスターをオフにするという余分な複雑さは解決策ですが、これにはコストが追加され、トランジスターのバイアスには依然として消費電力があります。別の解決策は、高電圧nチャネルデプレッション型MOSFETを使用することです(図1C)。これは高電圧からのゲートバイアスを必要としませんが、これらのコンポーネントは比較的まれで高価であり、そしていくつかの追加部品が必要です。

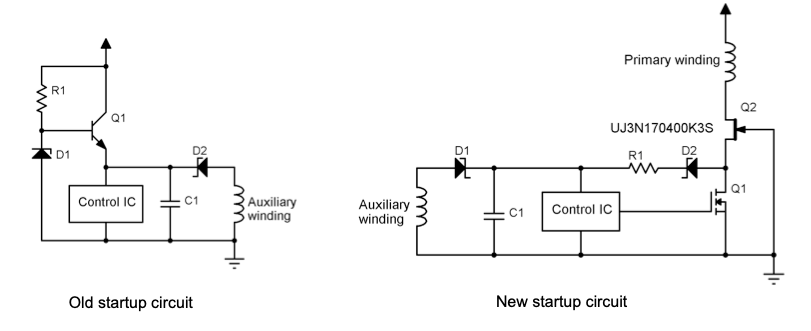

しかし、この問題に対する革新的な解決策があります。これは設計全体を再考する必要がありますが、複数の利点があります。制御ICは、カスコード構成でJFETと一緒に使用できる外付けMOSFETを駆動します(図2)。高電圧のSIC JFETを使用すると、非常に低い損失で劇的に高速にスイッチングでき、短絡や過電圧に対して非常に堅牢です。この構成のMOSFETは低電圧タイプでもよく、通常は30V定格です。

SiC JFETは通常ONであるため、ICの低電圧ロックアウトに達して回路が切り替わるまで、D2とR1を介してC1に電流を供給します。SiC JFETのソースは約10 Vを超えることはできませんが、これはSiC JFETのゲートが0 Vの状態でチャネルを遮断することになるため、R2を比較的低い値にすることで、損失をほとんど出さずに素早く起動することができます。D2は低コストで低電圧のダイオードです。その後、約12Vに設定された電源トランス上の巻線からの補助電源が引き継ぎ、スタートアップ回路でそれ以上の損失を発生させずにD2を逆バイアスすることができます。

低電圧MOSFETは余分なコンポーネントであり、低コストですが、制御ICのダイ上にあれば排除できます。実際、低電圧MOSFETは、ICの出力トランジスターへの駆動用としてすでに事実上存在している可能性がありますが、これを除去することでコストを再び節約することができます。さらに段階的には、SiC JFETダイを制御ICダイと一緒にパッケージ化することで、非常にコンパクトで費用対効果の高いソリューションを実現しています。QorvoのSiC JFETダイは、1700 Vまでの高電圧定格、140mΩまでの低RDS(ON)、800マイクロ平方までのダイサイズを備えており、このアプローチに最適な選択肢です。SiCは、シリコンの3.5倍の熱伝導率を持つ固有の高温定格を持っているため、ダイサイズが小さいにもかかわらず、一般的なICパッケージ内で非常に効果的に熱を伝えることができます。

そのため、「スタンバイ」モードをオフにしてください。 その190億ドルのあなたの取り分を主張し、同時にアイドリング機器の損失を減らすことにより、このエレガントな方法で少し地球を助けられるかもしれません。

お問い合わせ

本記事に関してご質問などありましたら、以下より問い合わせください。

Qorvoメーカー情報Topページへ

Qorvoメーカー情報Topページへ戻りたい方は、以下をクリックください。