NXP i.MX 8/9 DDR デザインガイドライン

メモリーインタフェースの高速化に伴い、ボード設計の厳密化への要求が高まっており、メモリーに関する動作不具合も増加傾向にあります。

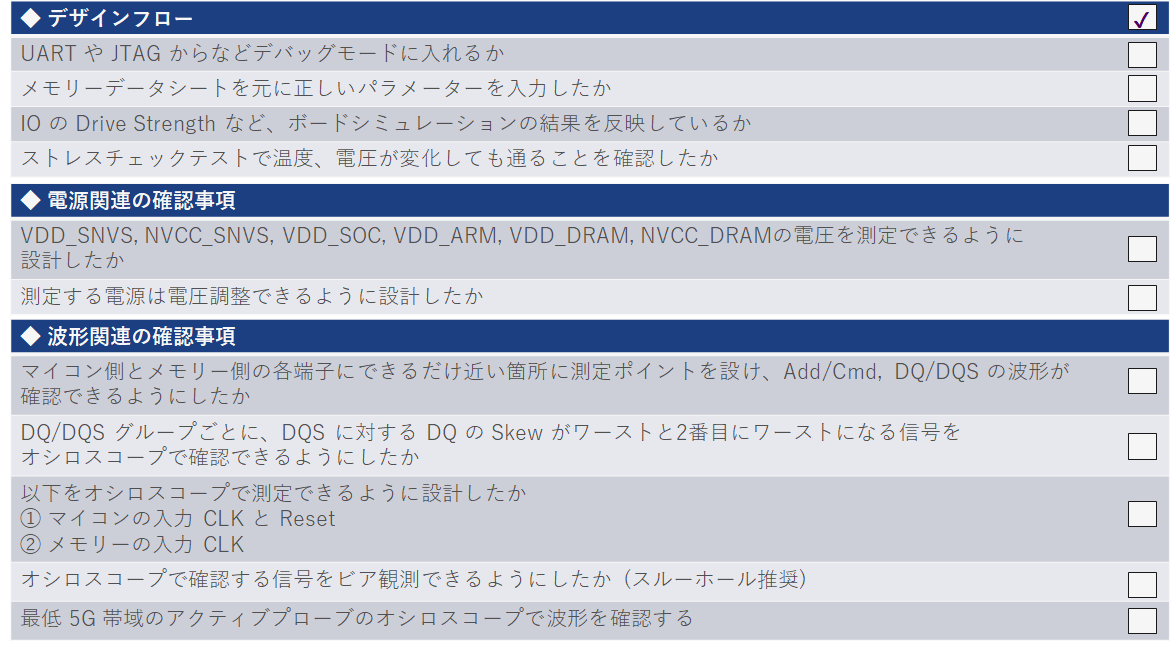

デザインフロー と デバッグフロー を示し、適切な手順で設計をおこなうことにより不具合混入を防ぐことと、デバッグ に必要な仕組みを実装することにより速やかに問題を解決することを目的に DDR デザインガイドラインをご用意しました。

設計時間の短縮、市場への不良流出の防止のためにガイドラインを守り、不具合のない製品を最短期間で市場に投入させましょう。

NXP i.MX 8 / i.MX 9 の DDR を設計する際に確認するべき点をまとめたデザインガイドライン資料となっております。DDR 設計の際に参考にしてください。

目次

1. はじめに

2. DDRデザインフロー

3. DDR デバッグフロー

4. Appendix

4-1. DDR Register Programming Aid

4-2. DDR Tool

4-3. DDR Stress Test

4-4. ボードシミュレーション結果の確認項目

4-5. i.MX 8/9シリーズと対応DRAM

弊社より資料を入手されたお客様におかれましては、下記の使用上の注意を一読いただいた上でご使用ください。

1. 本資料は非売品です。許可なく転売することや無断複製することを禁じます。

2. 本資料は予告なく変更することがあります。

3. 本資料の作成には万全を期していますが、万一ご不明な点や誤り、記載漏れなどお気づきの点がありましたら、弊社までご一報いただければ幸いです。

4. 本資料で取扱っている回路、技術、プログラムに関して運用した結果の影響については、責任を負いかねますのであらかじめご了承ください。

5. 本資料は製品を利用する際の補助的な資料です。製品をご使用になる場合は、英語版の資料もあわせてご利用ください。

NXP 提供の i.MX 8/9 Series DDR Tool

NXP WEB サイトやドキュメントに記載の情報もよく確認の上 i.MX 8/9 の DDR を設計ください。

i.MX 8/9 は Config Tools for i.MX (Pins Tool & DDR Tool) にて DDR 設定ファイルの生成が可能となっています。

お問い合わせ

本記事に関してご質問などがありましたら、以下よりお問い合わせください。

NXP Semiconductors メーカー情報Topへ

NXP Semiconductors メーカー情報Topに戻りたい方は、以下をクリックしてください。