Memory Base RegisterとMemory Limit Registerの使い方

PCIeインターフェースは、今では広く使われている技術ですが、規格書(PCIe Specification)だけでは少し分かり難いため、本コラムでは、規格書から抜粋したトピックについて説明していきます。

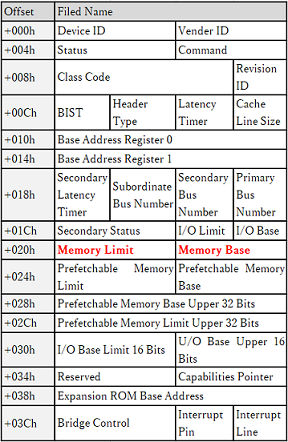

今回は、Type1 Configuration Space Headerの中で、Memory Base RegisterとMemory Limit Registerの使い方について説明します。Memory Base Register/Memory Limit Registerは、PCIe SwitchのようなBridge Deviceが、受け取ったMemory Transactionを通すか否かを判断するための、Memory Rageを設定するために使用します。

Registerに設定したMemory Range内のMemory Transactionであれば、そのMemory Transactionを通しますが、Memory Range外のMemory Transactionであれば、そのMemory Transactionを通さない、という動きになります。

Memory Base/Limit Registerの役割

Memory Base/Limit Registerの役割は以下となります。

・Memory Base RegisterとMemory Limit Registerは16bits、Memory Rangeは32bitsで構成されます。

・Memory Base RegisterはMemory Rangeの開始アドレスを設定し、Memory Limit RegisterはMemory Rangeの終了アドレスを設定します。

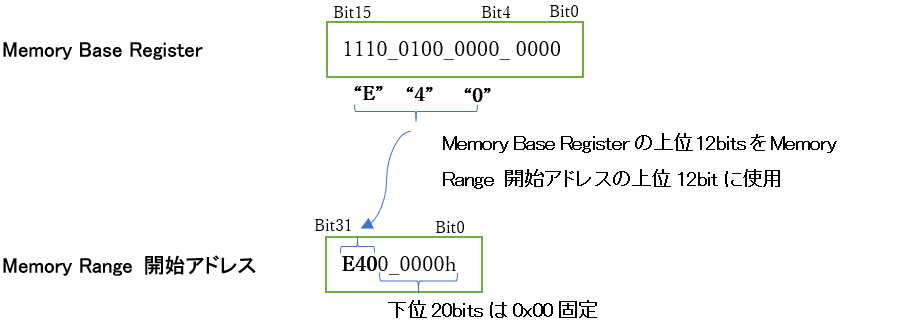

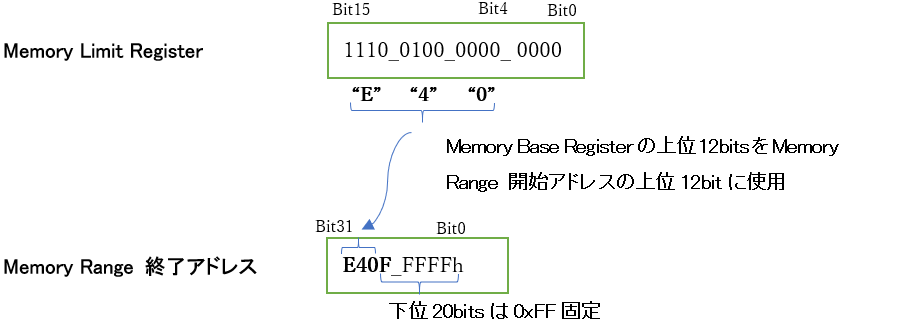

・Memory Base Registerの上位12bitsはMemory Rangeの開始アドレス上位12bits、Memory Limit Registerの上位12bitsはMemory Rangeの終了アドレス上位12bitsとなります。

・Memory Rangeの開始アドレス下位20bitsは0x00固定、終了アドレスの下位20bitsは0xFF固定となります。

設定方法の具体例

どのような値を設定すればいいのか、具体的な例を用いて説明します。詳細な仕様についてはPCIe Specificationをご確認ください。

Memory Transactionを通すMemory RangeをE400_0000h - E40F_FFFFhの範囲に設定する場合は、以下のようにRegisterを設定します。

上記のRegister設定により、E400_0000 - E40F_FFFFのMemory Rageを設定することができます。

お問い合わせ

本記事に関して、ご質問がありましたら以下より問い合わせください。