Ethernet PHYを実装したプリント基板(PCB)は、最もEMI・ ESD 及びその他全体のパフォーマンスに影響を及ぼす要因の一つです。本コラムでは、Ethernet PHY周辺回路の基板設計に関わる要点をいくつかご紹介したいと思います。

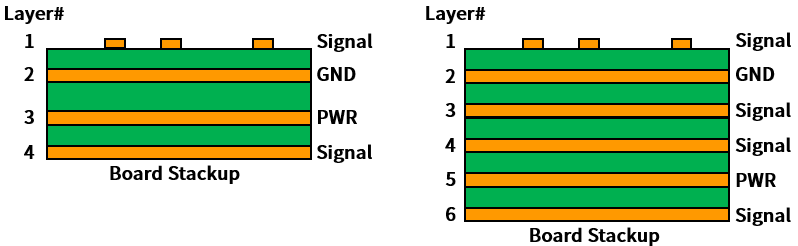

PCB Layer (Stackup)

Ethernet PHYを実装し、信号品質とパフォーマンスの要件を満たしたPCBを設計するには、少なくとも4層のPCBをお勧めします。図1は、4層 及び 6層のPCB Stackupの例です。

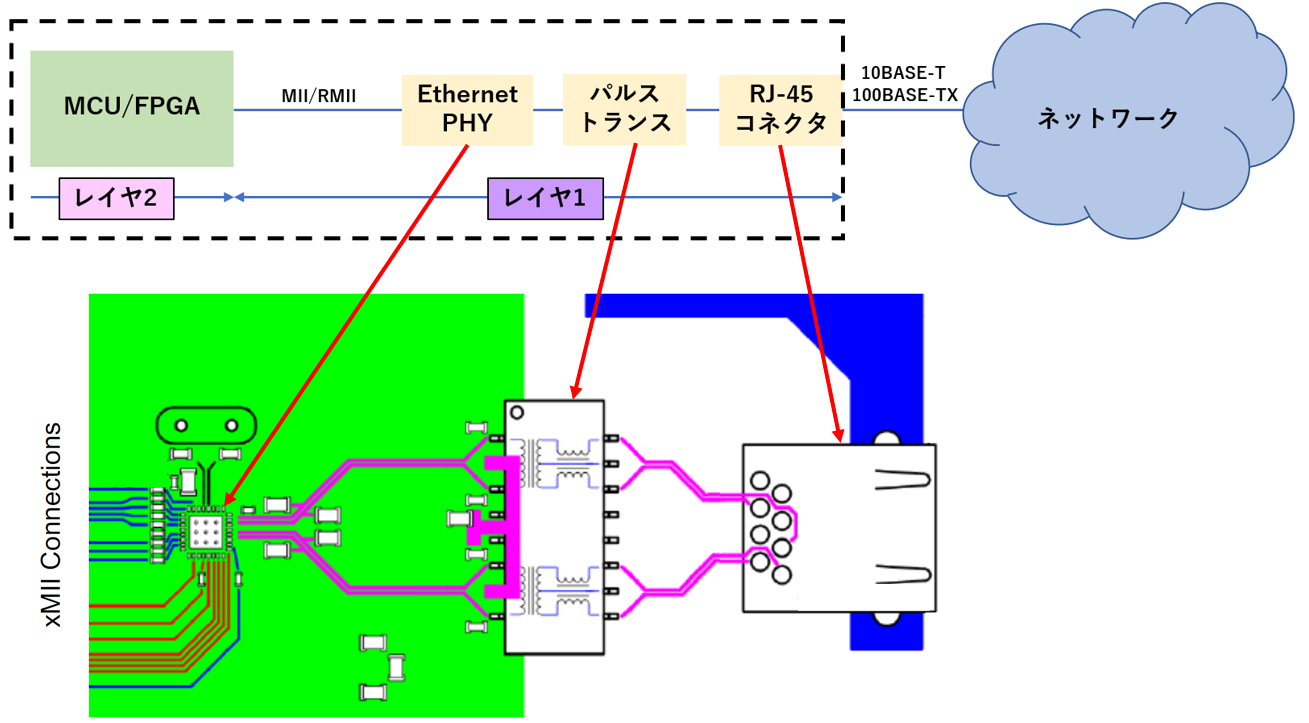

Ethernet Layout Example

図2は、一般的なEthernet InterfaceのH/W構成です。Layer2はMCUやFPGAで構成し、Layer1はEthernet PHY・パルストランス・RJ45コネクターで構成されます。

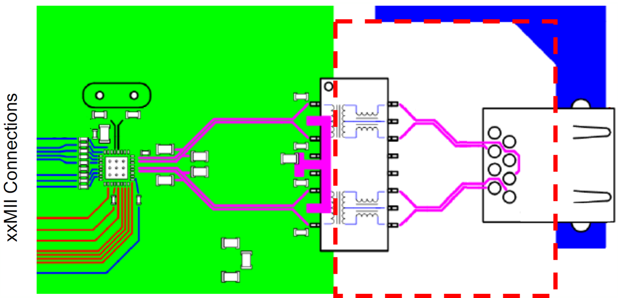

Transformer Area

図3は、Transformer Area(赤色破線で囲まれたエリア)です。Transformer AreaのPCB設計では、以下の点に注意します。

・全ての基板層の電源及びグランドプレーンはトランスの下への配置は避ける。

・シャーシグランドはトランスの先のRJ45まで延ばす。

・PHYとRJ45コネクター間にデジタル信号の配線はおこなわない。

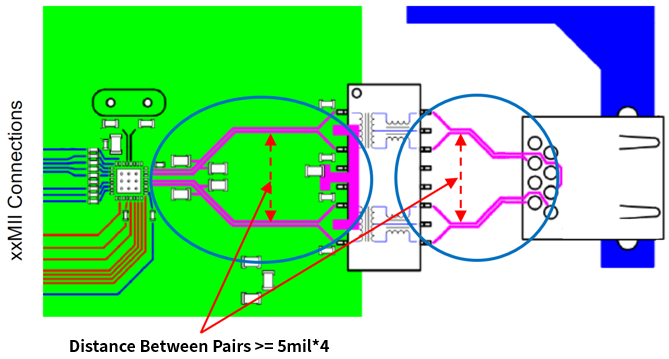

差動信号レイアウト

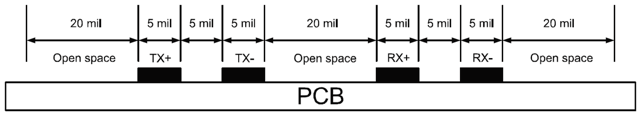

図4と図5は、差動信号レイアウトと送受信差動ペア信号配置 の例です。

信号品質とパフォーマンスの観点から、差動信号のレイアウトは非常に重要です。差動信号のレイアウトについては、以下の点に注意します。

・差動ペア(TX+/- or RX+/-) はその他の信号から離し、5milトレースで配線し5milトレースの間隔を持たせ、

等長配線で100Ωのインピーダンスにコントロールする。

・差動ペアのトレースは、できる限り短く対称となるように配線する。

・差動ペアは、同一基板層に配置配線する。

・スタブ(Stubs)はすべての信号トレース、特に差動信号ペアでは避ける必要がある。

・差動ペアは、お互い少なくとも5milトレース間隔の4倍以上離す。

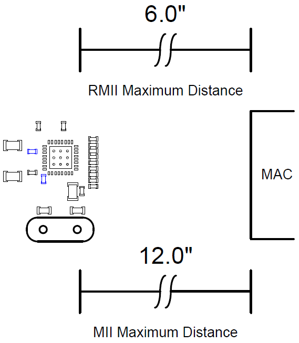

MAC Interface (MII/RMII)

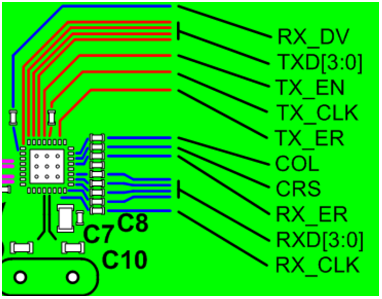

PHYとMACを繋ぐMAC InterfaceのLayoutにも、いくつか注意点があります。

・MII 及び RMIIの各信号は、68Ωのインピーダンスにコントロールする。

・送信信号グループと受信信号グループは、それぞれ一緒にトレースする。(図6参照)

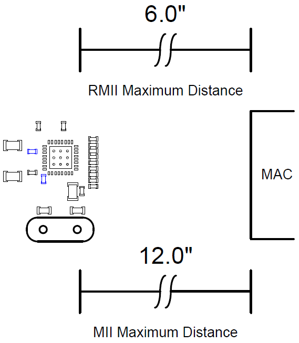

・MII 及び RMIIの各信号は、出来る限り最短でトレースする。

最大トレース長は、MIIで12inch以下、RMIIで6inch以下を推奨。(図7参照)

・配線を曲げるときは90度での曲げを避け、45度曲げとする。

まとめ

以上がEthernet PHY周辺回路のPCB設計をする際の基本的な注意点です。

ご設計に際しては、IC Vender発行のApplication NotesやH/W Design Checklistなどを確認することをお勧め致します。

Microchip社 Ethernet関連製品情報

Microchip社のEthernet関連製品情報は、以下をクリックください。

お問い合わせ

本記事に関してご質問などありましたら、以下より問い合わせください。

Microchip メーカー情報Topへ

Microchip メーカー情報Topページへ戻りたい方は、以下をクリックください。