Microchip 社 不揮発性 FPGAの特徴である【ソフトエラー(SEU)耐性】について、3回に分けてご紹介していきたいと思います。

第1回は、Microchip社 不揮発性 FPGA が、【なぜソフトエラーに強いのか?】についてご説明します。

ソフトエラーとは

ソフトエラーという言葉はご存知でしょうか?

1990年代以前、規則性や再現性が著しく低い頻度で発生する不具合を「ソフトエラー」と位置付け、原因不明の不具合として扱われている時期がありました。

2000年代になるとソフトエラーの原因が、中性子によるものということがわかってきました。近年では、SEU『エス・イー・ユー』という呼称も一般的になってきました。ソフトエラーとSEUは一般的に同意語として普及しているようです。ここで、SEUはSingle Event Upset『シングル・イベント・アップセット』の略語で、中性子の影響で発生する不具合を指し、SEUによって生じる不具合がソフトエラーであると言えると思います。

近年、SEUによる機器のトラブルによって、その解析と対策に多大な工数を取られるという話も聞き及んでいます。SRAMベースのFPGAを量産で使用する機会が増えSEUが問題になっている昨今、SEUに対して非常に堅牢なFlashベースFPGAの需要が高まってきています。

ソフトエラーに強いことで下記のようなメリットがあります。

- ソフトエラーの解析や対策の工数削減

- 信頼性の向上

これからMicrochip社のFPGAがなぜソフトエラーに強いのかについてご紹介していきたいと思います。

FPGAのコンフィグレーション・テクノロジーの比較

はじめに、PLDは以下のテクノロジーに大別されます。

- アンチヒューズ

- 紫外線消去型 (EPROM)

- 電気的消去型ROM (EEPROM、Flashメモリー等)

- スタティックメモリー(SRAM)

3、4は現代FPGAで広く利用されているプログラミング・テクノロジーになります。

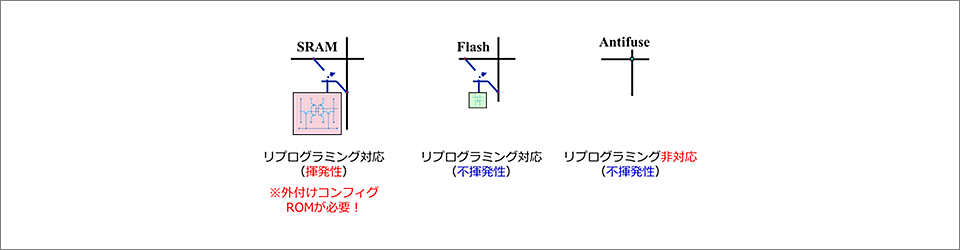

次にFPGAの配線テクノロジーの比較を下記に示します。

SRAMは揮発性になるので、外付けコンフィグレーションROMからのプログラミング(ダウンロード)が必要になります。Flashは不揮発性になるので、直接Flashセルにプログラミングします。

Antifuseは、ヒューズの名の通りプログラムで接点を溶融することで接続します。

注)ヒューズは溶断(断線)ですが、“アンチ”ヒューズは溶着(接続)になります。

一般的にSRAMはSEUに大きく影響を受けることが知られています。一方、Flashは方式や構造によってはSEUによる影響を大きく軽減することができます。Antifuseに至っては、接点を溶融するほどのエネルギーがSEUによって発生するとは考えられませんので、影響を受けることはありません。上記より中性子に起因するSEUの観点では、Antifuse = Flash >> SRAM のような位置づけと考えられます。

つづいて、FlashベースFPGAがなぜソフトエラーに強いのか?についてご紹介します。

なぜソフトエラーに強いのか?

Microchip FPGAがソフトエラーに強いのかの主な理由として下記の2点が挙げられます。

- 構造の作り込みによる耐性

- Flashベース・テクノロジーによる耐性

まずは、1.から説明していきます。

1. 構造の作り込みによる耐性

ここでFlashベースFPGAの構造をご紹介します。

一般的なフラッシュ・メモリーはFlashセルでデータ自体を保持しています。例えばMLC(Multi Level Cell)方式の場合は11~00の4値を保持します。

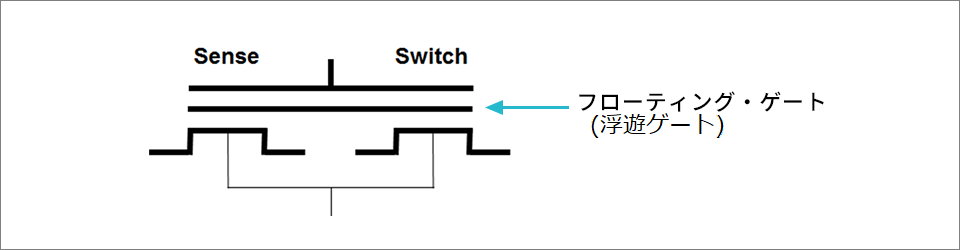

一方、FPGAのFlashセルは一般的なフラッシュ・メモリーのFlashセルとは異なり、配線構造のスイッチとして機能します。下記にMicrochip FPGAのFlashセル構造の代表例を示します。

一般的なフラッシュ・メモリーとは異なり、いわゆる2TタイプのFlash構造になっており、フローティング・ゲートを共有し物理的な大きさも兼ね備えています。“Sense”側のFlashセルはプログラム(ライト)の役割を担います。一方、“Switch”側のFlashセルは論理動作(配線スイッチ)の役割を担っています。

上記を含め、FlashベースFPGAでは以下のような構造的な工夫が盛り込まれることで、大幅な信頼性の向上をもたらしています。

- フローティング・ゲート(浮遊ゲート)がSense と Switchで共有化され、10倍多くの電荷をストア

- 厚いトンネル酸化膜

- プログラム(ライト)回数の制限

次に、2.を説明していきます。

2. Flashベース・テクノロジーによる耐性

ご存知のようにFlashセルはErase(チャージ)とProgram(ディスチャージ)を1サイクルとして、浮遊ゲート(Floating Gate)に電荷をチャージ/ディスチャージして“0”、“1”をプログラムします。通常、EraseとProgramの動作は非常に高電圧で実施しています。

一般的にSEUによって発生するエネルギーは5V前後と考えられており、FlashベースFPGAのEraseやProgramの高電圧からすると、5Vから受ける影響は、ほぼ無視できる程度であると言えます。このようにFlashベースFPGAのテクノロジーはSEUに対し理想的な耐性を備えていると言えます。

まとめ

Microchip社のFPGAがソフトエラーに強い理由としては、下記になります。

1. 構造の作り込みによる耐性

- フローティング・ゲート(浮遊ゲート)がSense と Switchで共有化され、10倍多くの電荷をストア

- 厚いトンネル酸化膜

- プログラム(ライト)回数の制限

2. Flashベース・テクノロジーによる耐性

さらに、ソフトエラーに強いということは、下記のメリットが得られます。

- ソフトエラーの解析や対策の工数削減

- 信頼性の向上

以上、【なぜソフトエラーに強いのか?】でした。

お問い合わせ

本記事に関してご質問などありましたら、以下より問い合わせください。