本コラムでは、プリント基板にFPGAを実装する際にスペース面でお困りの方を対象に、

Microchip FPGAの特徴である【省スペース】についてご紹介していきたいと思います。

省スペース

『SRAMベース』と『Flashベース』FPGA

現在普及している多くのFPGA(Field Programmable Gate Array)は、『SRAMベース』になります。Microchip社からは主に『Flashベース』FPGAが提供されています。

同じFPGAでも『SRAMベース』と『Flashベース』では、特徴に様々な違いがあります。

いくつかの本関連サイトでもご紹介しているように、『SRAMベース』と『Flashベース』のFPGAを比較した場合に次の大きな特徴の違いが見られます。

◇SRAMベースFPGA:

電源OFFで、書き込まれたデータが消去される。

◇FlashベースFPGA:

電源OFFでも、書き込まれたデータは消去されない。

ブート用ROM

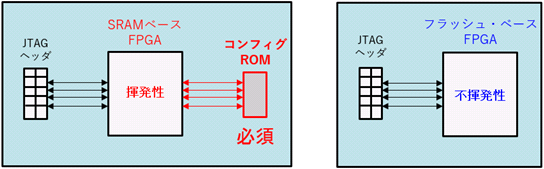

SRAMベースFPGAは、概ね、ブート用の『コンフィグレーションROM』が必要ですが、Flashベースの場合、ブート用ROMは不要で『不揮発性FPGA』とも呼ばれています。

そのため、Microchip社のFPGAは、今までROMに割かれていた実装スペースを見直すことが出来ます。それぞれのケースにおける、基板の実装イメージを図1に記します。

省スペース・パッケージ

FPGAの選定にあたり、サポートされるロジック規模(LE数)、I/O数、それにパッケージ・サイズのバランスは非常に重要なポイントになります。

特に、スペース面での制約が非常に厳しい基板へFPGAを実装する際、コンフィグROMの削減はもとより、ある程度のロジック規模を維持しながら省スペース・パッケージのFPGAに関する需要は多いと思われます。

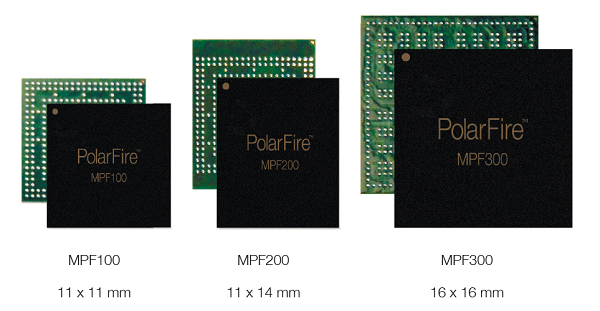

Microchip社の不揮発性FPGA『PolarFire™』は100~500K個のロジック・エレメント規模のミッドレンジの性能を維持しながら、小パッケージ品の100K、200Kおよび300K個のロジック・エレメントを使用することが出来ます。

そのパッケージ・イメージを図2に記します。

特に、マシン・ビジョン系のカメラ・アプリにおいては極めて小さな基板上に、イメージ・センサー、FPGA、SDRAM等の周辺部品を実装しなければならないため、『PolarFire™』はそれらのアプリを実現する上でのキーパーツとも言えます。

電源シーケンス回路

SRAMベースFPGAの場合、電源印可時に伴う突入電流(イン・ラッシュ・カレント)の問題が取り上げられており、製造プロセスの微細化に伴いその電流値は増加傾向にあります。

より微細化されたSRAMベースのFPGAでは、予めメーカーから指定されたコアやI/O用のパワー・シーケンスを守った電源投入や遮断が必要になります。そのため、CPLD(Complex Programable Logic Device)やディスクリート部品を用いたシーケンス回路の実装が必要になります。

一方、Microchip社FlashベースFPGAの場合、突入電流の観点でメーカー側から電源シーケンスの指定はありません。従って電源シーケンス回路のスペースが削減可能です。

まとめ

前述のとおりに、FlashベースのFPGAをご利用頂くことで基板サイズのシュリンクや装置自体の更なる小型化が可能になります。

また、スペース・メリット以外に下記3点のメリットも挙げられます。

1)コスト削減<高価なコンフィグROM>

2)工数削減<コンフィグROMのディスコン対応>

3)工数削減<コンフィグ・エラー発生時の対応>