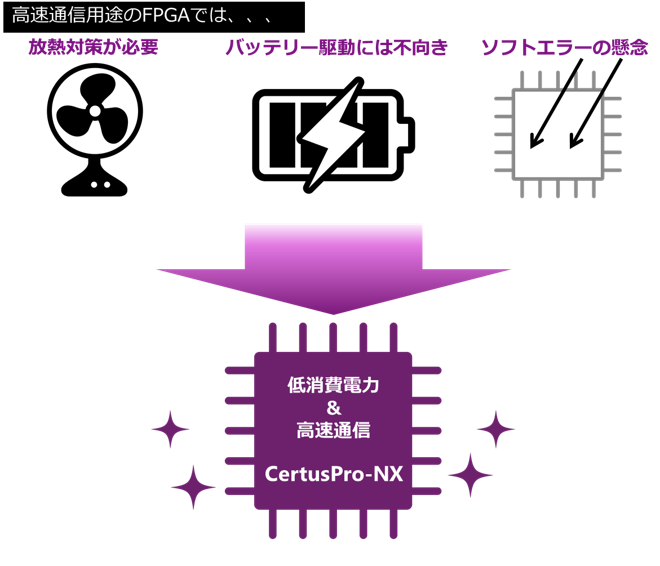

設計者が自由に論理回路を変更できるFPGAは、高速通信が求められる製品開発で多く採用されています。一方で「消費電力が多く、放熱対策が必要になるため、製品の筐体が大きくなってしまう」「バッテリーで動く機器には向かない」「ソフトエラー対策に手間がかかる」といった技術者の声も聞かれます。

こうした課題をお持ちの方に向けて、低消費電力と高速処理を両立した小型パッケージのFPGAを紹介します。

柔軟な回路設計が可能。高速通信に対応するFPGA

データ通信技術や映像技術の発展にともない、PCIe、CXP、SLVS-ECといった高速インターフェース規格が登場し、高速通信に対応できる製品が市場に求められています。また、IoT技術が普及するにつれて、AI推論エンジンを端末に組み込むエッジAIへの期待が高まるようになりました。こうした中、高速処理が可能で、柔軟に回路を設計でき、機能の差別化を図れるFPGAが幅広い製品開発で採用されています。

一方、FPGAのデメリットとして、消費電力や発熱の大きさが挙げられます。そのため、人体と接触する医療機器、長時間稼働する産業機器、バッテリーで稼働するIoT機器やモバイル機器などには不向きだと考えられてきました。このたび、ラティスセミコンダクター社がリリースした汎用FPGA「CertusPro-NX」は、FD-SOIプロセスによって高速通信、高速処理、低消費電力を実現しました。発熱も大幅に抑制できます。これまでFPGAを利用しづらかった製品にも展開することが可能です。

近年、主流となっているFinFETプロセスは、3Dトランジスター(立体トランジスター)で構成され、高速スイッチ動作や高集積化ができるのが特徴です。しかし、クロックの周波数が上がれば消費電力も上がり、集積度が上がれば単位面積当たりの発熱も上がることが懸念されます。

それに対し、FD-SOI(完全空乏型シリコン・オン・インシュレーター)は「埋込酸化膜」と「超薄型シリコン膜」を使用したプレーナー型トランジスターで構成されています。埋込酸化膜によりソース・ドレイン間の電子の流れを効率化でき、超薄型シリコン膜によりトランジスターのON/OFF制御(チャネル・ドーピング)が不要になります。そのため、リーク電流を大幅に低減できるのが特徴です。

3Dトランジスター(立体トランジスター)の構造

完全空乏型トランジスターの構造

従来のFPGAの課題は「消費電力」「発熱対策」「ソフトエラー対策」

CertusPro-NXの活用例として、下記のような用途が挙げられます。

<活用例>

・内視鏡など映像通信をともなう医療機器に活用。低消費電力のため発熱が少なく、人体に接触する製品にも安全に利用できる。

放熱部品が要らないため、コンパクトな製品サイズを実現できる。

・VR、ARなどのヘッドマウントディスプレイに採用し、サイズや発熱の観点から、長時間装着できる製品を実現する。

・産業用マシンビジョンシステムなど、高解像度と高速通信が求められる機器を開発する。

・生産工場や化学プラント、車載デバイス、宇宙系事業など、ソフトエラーによる誤作動が許されない製品に利用し、開発工程を省力化する。

・モバイル機器などのASICといった専用ICと、FPGAを組み合わせて、次世代技術に対応する新製品を短期間で開発する。

従来、こうした製品開発にFPGAを利用する際には、次の課題が生じていました。

課題(1) 消費電力の大きさ

一般的なFPGAは消費電力が大きいため、バッテリーの持ちが悪くなります。また発熱も大きいため、医療機器やヘッドマウントディスプレイなど、人体への接触をともなう製品には利用しづらい面がありました。

課題(2) 放熱部品の組み込み

FPGAからの発熱が大きいため、ヒートシンクやファンといった放熱部品が必要になる場合が多くあります。製品筐体が大きくなってしまい、コストアップ要因にもなっていました。

課題(3) ソフトエラー対策

一般的なFPGAはSRAM構造になっており、宇宙線に由来する中性子線によって、ビット化けが発生します。予期せぬ誤作動を防ぐためのソフトエラー対策に手間がかかっていました。

FD-SOIプロセス採用。医療機器・産業機器・IoT機器に使える小型FPGA「CertusPro-NX」

ラティスセミコンダクター社の高度な汎用FPGA「CertusPro-NX」は、下記の特長を持ち、これまでFPGAを積極的に使用できなかった分野からも関心を集めています。

特長(1) FinFETに比べ、約1/4の消費電力を実現

FD-SOIプロセスの採用により、消費電力の大幅な削減を実現しました。FinFETプロセスによる同規模のFPGAと比較して、約1/4まで消費電力を抑えています。発熱そのものを大幅に抑制できるため、放熱対策が不要です。

特長(2) 最大10.3Gbps、競合の約2倍の帯域幅を提供

最大10.3GbpsのSERDES回路を採用し、同規模FPGAと比較して、約2倍の帯域幅を実現しています。PCIe、CXP、SLVS-ECなど、さまざまなプロトコルにも対応しています。

特長(3) AI実装にも最適なメモリー構成

同規模FPGAと比べて約65%も多くのブロックメモリーを搭載し、AI実装にも最適な構成となっています。LPDDR4をはじめとする外部メモリーも接続可能です。

特長(4) ソフトエラーレートを約1/100に抑制

FinFETプロセスと比較して、ソフトエラー発生率を1/100程度まで抑制できます。24時間稼働し続ける産業用ロボットや、誤作動が世界中に影響するプラント事業、車載デバイス、宇宙系事業に使われる製品にも最適です。

特長(5) パッケージサイズを1/6以下に小型化

CertusPro-NXのパッケージは9ミリ角、面積にして81平方センチメートルという小ささを実現しています。他社の同規模FPGAでは529平方センチメートルの製品もある中、およそ1/6以下のパッケージサイズを実現しました。カメラやIoT機器など、筐体をコンパクトにしたい製品にもうってつけです。

製品仕様

|

Features |

CPNX-50K ※1 |

CPNX-100K |

|

|

Logic Cells |

53K |

96K |

|

|

EBR |

1.7 Mb |

3.7 Mb |

|

|

Large RAM |

2 Mb |

3.6 Mb |

|

|

DSP (18 × 18 Mults) |

96 |

156 |

|

|

PLLs |

3 |

4 |

|

|

Hard Blocks |

10GE PCS, PCIe Gen 3, SGMII CDR, ADC |

||

|

Packing |

I/O (WR + HP + ADC) ※2 |

||

|

ASG256 (0.5mm pitch) |

9 × 9 mm |

170 (TBD) ×4 SERDES |

165 (75 + 84 + 6) ×4 SERDES |

|

CBG256 (0.8mm pitch) |

14 × 14 mm |

170 (TBD) ×4 SERDES |

165 (75 + 84 + 6) ×4 SERDES |

|

BBG484 ※3 (0.8mm pitch) |

19 × 19mm |

230(TBD) ×4 SERDES |

305 (167 + 132 + 6) ×8 SERDES |

|

BFG484 ※3 (1.0mm pitch) |

23 × 23 mm |

230(TBD) ×4 SERDES |

305 (167 + 132 + 6) ×8 SERDES |

|

LFG672 (1.0mm pitch) |

27 × 27 mm |

305 (167 + 132 + 6) ×8 SERDES |

|

※1:CPNX-50K information is preliminary

※2:WR: Wide-Range I/O, HP: High-Performance I/O, ADC: Dedicated ADC inputs

※3:SERDES speed limited to 6.25 Gbps in BBG484 and 5.5 Gbps in BFG484