第2回:DDR 2 をどうやって設計検証するの?

≪目次≫

|

|

≪DDR2 SDRAM インタフェース≫

USB 3.0 と言うことでコラムを書かせていただいていますが、高速シリアル・インタフェースとは切っても切れない関係にいるのが、メモリの存在です。データの大容量化に伴い信号の高速化が見られる中、メモリ・インタフェースも例外ではなく、高速化が求められています。『5Gbps で通信できる!!』と言っても肝心のデータをメモリに格納するのに数百 Mbps だと、宝の持ち腐れになってしまいます。

そこで、Cyclone® III USB 3.0 Board には、DDR2 – 400 SDRAM x16bit を 2チップ搭載し、USB 3.0 の帯域である、5Gbps に余裕を持って追従できる転送レートを持っています。また、後になりましたが、DDR2 と言うのは ダブル・データ・レート(DDR)という高速転送機能の一つであり、クロック信号の立ち上がり時と立ち下がり時の両方でデータの読み書きが行なえ、通常の倍の転送速度が実現できます。最近ですと “DDR3” などが出てきて、さらにメモリに対するインタフェースの高速化が進んでおります。

しかし、信号線はシングル・エンドのパラレル・バスな上、規格では、配線長などは細かく決められておらず、意外と設計者泣かせなところがあります。

そこで、今回は、USB 3.0 をご紹介をする前に DDR2 SDRAM インタフェースのトポロジー検証を実際の事例を交えてご紹介をいたします。

≪FPGA を使用して、DDR2 SDRAM インタフェースの実現≫

FPGA にデザインとして組み込むDDR2 コントローラ・デザイン設計方法も気になると思いますが、まず基板設計です。基板設計がしっかりしていないと FPGA 内部のデザインどころではありません。また、回路図入力を行う前に DDR2 バスのトポロジーを検討する必要があります。

まず、DDR2 バス 信号をAddress/Command Group、DATA Group、Clock Group と各グループに整理し、グループごとに以下のようなトポロジーに決定しました。また、全ての DDR2 信号は等長配線とし、各終端抵抗、ダンピング抵抗は出来る限りピンの直近に設置するものとします。

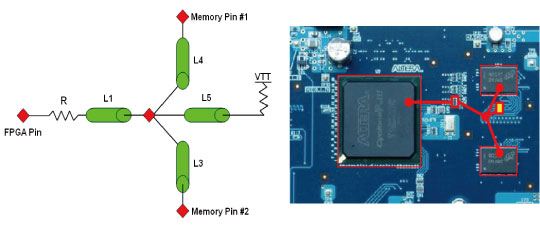

最初にAddress/Command Group です。Address/Command Group は、FPGA からの出力信号で I/O 規格が SSTL18-Class I になります。FPGA の送信端側にダンピング抵抗を設置し、DDR2 SDRAM の受信端側で Fly-By 終端抵抗を設置します。ここで、FPGA の送信端側のダンピング抵抗を FPGA が持っている内部抵抗 (On-Chip- Termination)に置き換えることが可能です。下記の図(Fig.1)は、外部にダンピング抵抗を置いた場合のAddress/Command Group のイメージ図になります。

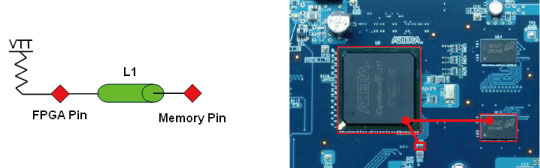

次に、DATA Group です。DATA Group は双方向の信号になり、I/O 規格も SSTL18-Class II になります。双方向信号になるので FPGA、SDRAM 両側に Fly-By 終端抵抗が必要になります。また、DDR2 SDRAM 側の Fly-By 終端抵抗を DDR2 SDRAM の内部抵抗 (On-Die-Termination) に置き換えることが可能です。下記の図(Fig.2)は、DDR2 SDRAM の内部抵抗を使用した場合のDATA Group のイメージ図になります。

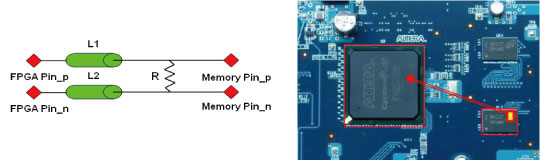

次に、Clock Group です。Clock Group は、差動信号であり、DDR2 チップの直近で、100 Ωの差動終端が必要になります。

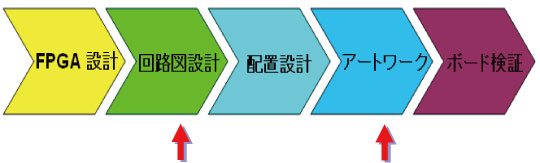

このような、決定したトポロジーを元に回路入力を行い、次にパターン設計行うのですが、このときに『信号品質』という問題にぶつかります。DDR2 などの高速信号を実現させるボード設計の場合、基板設計の各フェーズで高速信号に対応した設計手法を取り入れる必要があります。しかし、高速信号では信号のアナログ的動作が数々発生し、過去の経験則だけでは十分に対応仕切れない場合が出てきます。そのため、高速信号の設計になってきますとシミュレーションで事前検証を行うことが後戻り工数削減の重要なポイントになってきます。

そこで、基本的に伝送シミュレーションは、以下の図(Fig.4)の通り、Pre と Post で2回行います。まず、Preシミュレーションでは、トポロジー、部品配置の検証、また、抵抗値の見積もりなどで使用します。

次に Post シミュレーションでは実装設計後に、設計が適切かどうかを検証します。また、シミュレーションでは、どこにでもプローブが当てられるだけではなく、抵抗値・配線長などの値も自由にその場で変更できるので最適な基板設計が行えます。そこで、弊社の方で、HyperLynx® を使用し、IBIS を用いた伝送シミュレーションを行いました。Cyclone III のIBIS は、アルテラ社のホームページからもダウンロード出来ますが、Quartus® II でもユーザの設定(ピン名・ピンオプション etc ・・・ )が反映された、IBIS を生成出来ます。

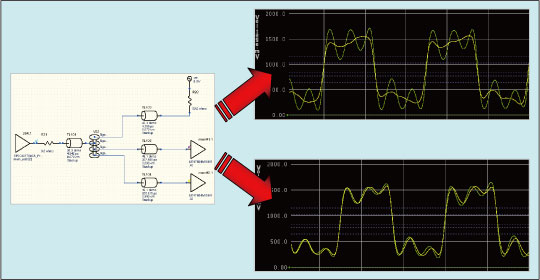

下記の図(Fig.5)は、1つの FPGA に対して、2 つの DDR2 SDRAM を搭載した時のシミュレーションになります。右の波形が上下で異なるのがわかります。これは、スタービアの分岐点から DDR2 SDRAM までのそれぞれの配線の差分が 1mm (右上) の結果と、0.5 mm(右下) の結果になります。

このように 0.5 mm の誤差なので見落としがちな部分ですが、伝送シミュレータを使用することで、改善することが出来ます。また、改善にかかる工数もシミュレーションなので抵抗・コンデンサ・配線長などの値も簡単に変更できますので、基板を作成し終わった後にデバッグするのと比べると格段に少なくなります。

このように伝送シミュレータを用いることで、重要な部分にも関わらず検証を行いにくかった部分が非常に簡単に検証できます。また、伝送シミュレーションは、DDR2 SDRAM インタフェースだけではなく、基板上における全トポロジーをも検証できるので、信号品質が起因する問題を大幅に削減できると考えております。

大変お待たせいたしました!次回は、USB 3.0 の設計・検証 をご紹介いたします。最終回です。お見逃しなく!