はじめに

こんにちは!くらみぃです。

FPGA を用いた制作実習を行っていく中で、新たな疑問が生まれました。

その疑問とは、「自分の作ったデザインが、使用予定である FPGA のロジック容量を超えないかな…」というものです。

この疑問に対して色々調べた結果、結論として

Quartus® Prime に作ったデザインを登録し、そのデザインを Compile してみないと、自分のデザインがどれだけのロジック数をもっているかわかりません。

よって、使用予定である FPGA のロジック容量超えるかどうかもわかりません。

しかし!!

事前に概算する方法がいくつかあり、いろんなパターンについて考えてみました。

1. 以前作ったデザインを改良した場合

2. 新しくデザインを作成する場合

3. Nios® II を使用した場合

4. SoC デバイスを使用した場合

1. 以前作ったデザインを改良した場合

まず、新たに追加したい機能のロジック数を概算します。

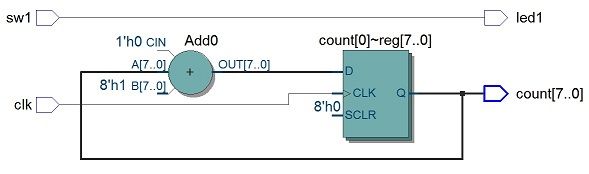

例えば、 CLK に対してカウントアップを続ける 8bit Counter 回路と、スイッチを押すと LED が光る回路を追加するなら、以下のような図をイメージできるかと思います。(図 1 )

図 1 をイメージし、おおよそのロジック数を概算します。

そして、以前のデザインの総ロジック数に、追加する機能のロジック数を足した値が、改良後のロジック数の概算です。

2.新しくデザインを作成する場合

こちらは概算のしようがないので、一度 Quartus Prime で Compile してみないとわかりません。

その際、フルコンパイルを実行すると、配置配線をした後の総ロジック数がわかります。

配置配線前の段階で、ロジック数の見積もりを行いたい場合は、論理合成後のロジック数を確認します。

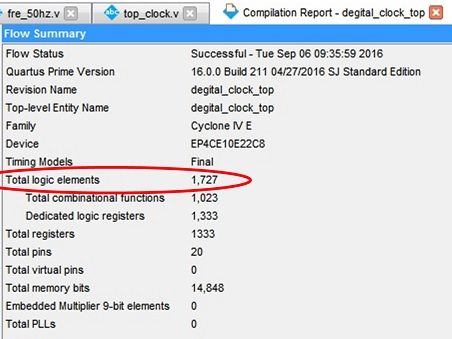

Quartus® Prime にて Start Analysis & Synthesis を行った後の Compilation Report を見てみます。(図 2)

図 2 より、配置配線する前の Total logic elements が 1727 あることがわかります。

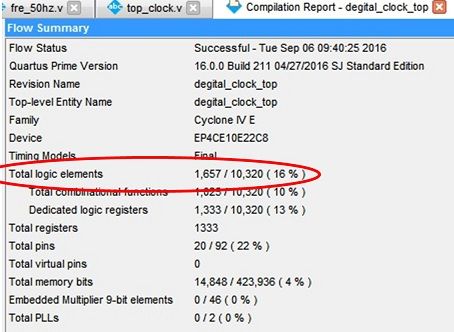

続いて Start Compilation を行った後の Compilation Report を見てみます。(図 3 )

図 3より 、配置配線した後の Total logic elements が 1657 あることがわかります。

配置配線した後の Report ですと、このデザインが FPGA のロジック容量の何%を使用しているかが分かりますね。

ここでさらに疑問が出てきます。

なぜ配置配線の前後でロジック数が異なるのでしょうか。

配置配線前のロジック数は、論理合成の結果から導いた見積もりのロジック数です。

それに対してフルコンパイル後は、配置配線がすべて終わった後の結果なので、実際に使用されるロジック数が確認できます。

このようにレジスタ・パッキングなどの最適化により配置配線後のロジック数は変わります。今回はフルコンパイル後のほうがロジック数が少なくなりましたが、必ず減少するというものではないのでご注意を。

3.NiosII を使用した場合

私も Nios II を使用した製作実習に取り組んでいますが、この Nios II を使用した時のロジック数はどのくらいになるのでしょうか?

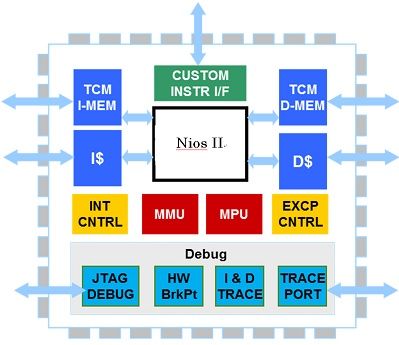

Nios II とは ALTERA のソフトコア CPU です。

この“ソフト”とはソフトウェアのことではありません。 FPGA のロジックを使って CPU を構成する、という意味の“ソフト”です。

CPU の回路が最初から FPGA に入っているわけではありません。 Nios II を FPGA に実装する際は FPGA のロジック領域を使用します。

Nios II は CPU ですので、単体では機能しません。

したがって、他に必要な Peripheral IP を組み込みますが、その IP のロジック数の分、 FPGA のロジックが使われます。

また、 Nios II と IP をつなげるためにバスも必要なので、バスの容量も使われます。

よって、 Nios II を FPGA に実装する際に使うロジック容量はNios II を実装する際の総容量 = Nios II 単体の容量 + 使う IP の容量+バスの容量となります。

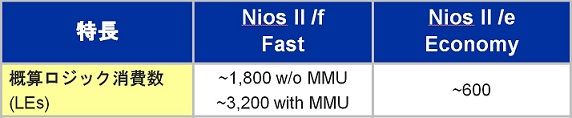

表 1 が、 Nios II における Economy / Fast の場合のロジック見積もり表です。

4. SoC デバイスを使用した場合

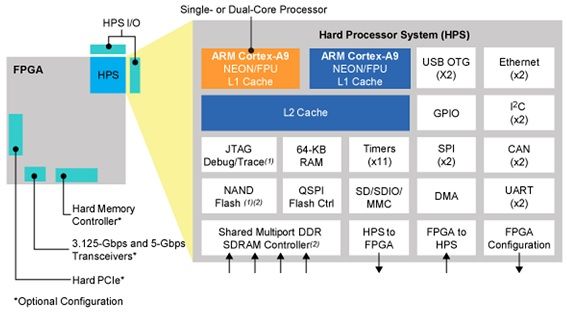

こちらはすでに SoC デバイス内に [HPS] (単語帳:Hard Processor System [HPS]、 CPU (ARM) と周辺回路を含むシステム)部分が組み込まれています(図 6)。

[HPS] 部分は決まった回路なので、 FPGA のリソースには影響しません。

つまり SoC デバイスのロジック数は、 FPGAに実装する回路のみで決まります。

終わりに

これで自分の作ったデザインに対して、どんなロジック容量を持った FPGA を選べばいいかわかりました。

次回記事もぜひご覧ください!