はじめに

こんにちは。少しずつ電子回路の世界に慣れてきたなみぃです。

最近は少しずつお客様対応をしながら、先輩から出された課題に取り組んでいます。

前回は インテル® FPGA 開発ツール(旧アルテラ FPGA 開発ツール) であるQuartus® の便利機能についての記事 を書きました。

『 Quartus でのピン配置 ~テキストベースが好きな人へ~ 』

今回は論理回路設計の際に役に立つ IP (Intellectual Property)を初めて使った時に失敗してしまったエピソードについて書きます。

ある日、キットの使い方や HDL (ハードウェア言語) に慣れるための課題がとぷぅ先輩から出されました。

とぷぅ先輩「LED が点滅する回路を作り、ボタンを押す毎にクロックの周波数を1MHz 、50MHz、150MHz と切り替え、LED の点滅スピードを変えてみよう」

私「何か条件はありますか ?」

とぷぅ先輩「クロックの切り替えに関しては ALTCLKCTRLという IP を使おうか」

私「ついに IP を使う日が来たのですね!」

IP とは?

そもそも IP とは「設計済みの機能回路ブロック」のことで、単体で専用の機能を有しているのです。今回は PLL を例にして説明します。

PLL とは入力されたクロックの周波数を変える(分周、逓倍)ことの出来る回路です。

PLL についてはこちらの記事もご参照ください。

『 バッファについて 』

これを 1 から HDL で記述して作るのは大変だし、時間がかかりますね…。

そんな悩みを解消するために IP があるのです。

インテル® FPGA には ALTPLL という PLL の機能を有している IP があります。

これを使えば使用するクロックを指定するだけで簡単に周波数の変更を行えます。

PLL に限らず多種多様な機能を持った IP が出されています。

非常に便利!

ちなみに IP の使用法はとぷぅ先輩が記事にしてくれていますのでこちらもご参照ください。

『IPをつかってみよう~IPの中身を見たい~』

私は当初 「IP をたくさん使えば簡単に課題をクリア出来るじゃあないか!」

…と考えていましたが、現実はそう甘くはありませんでした。

無知がゆえに何度も失敗しました。

その悲しいエピソードの前に ALTCLKCTRL の説明をします。

ALTCLKCTRL

ALTCLKCTRL は動作クロックの切り替えをする際に使う IPです。

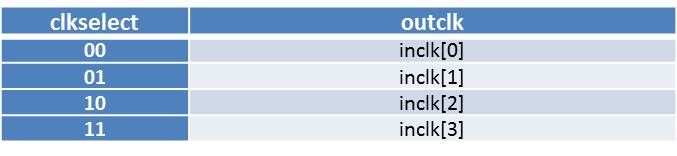

図2のようなブロックになっており「clkselect」の状態によって出力するクロック信号を切り替えています。

今回は元の周波数

・50 MHz

と PLL から出力された

・1 MHz

・150 MHz

の合計 3 つの周波数を ALTCLKCTRL に入力して切り替えればいいのですね!

やはり簡単に出来る気がしてきました!

接続する上での注意

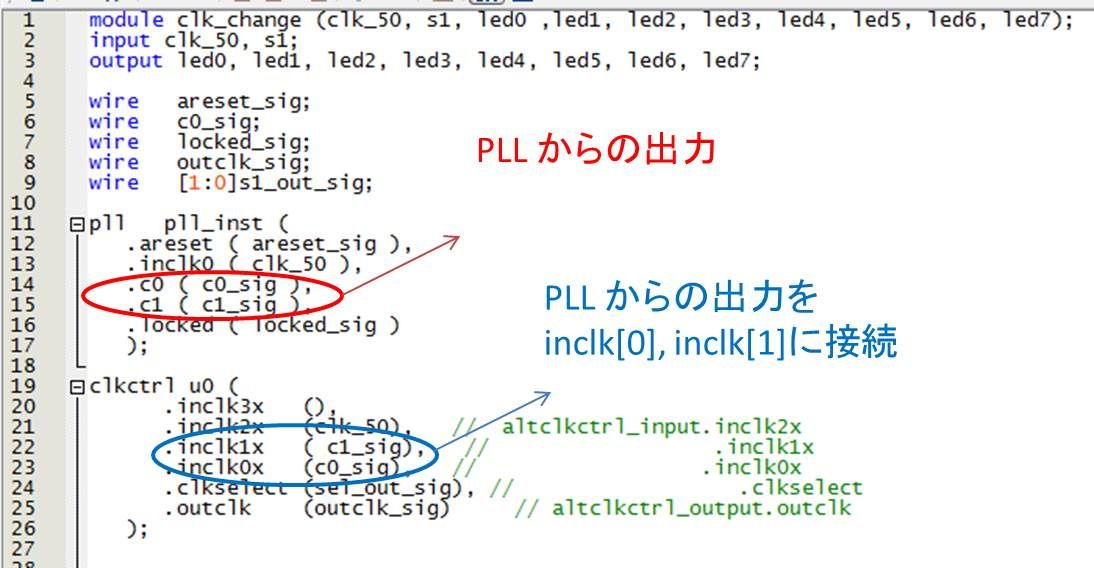

というわけで、最初は特に何も考えずに適当に接続を行いました(図3)。

しかし、コンパイルをすると…。

あれ?あれれ?

なんだ、このエラーは?(図4)

ヘルプを見てみると、どうやら入力に対して無効な信号が入っているとの記載が…。

クロック信号を入力しているのに無効とはどういうことだ…。

こんな時はユーザガイドしかない!読み進めているとこんな項目が…。

ALTCLKCTRLのユーザガイドはこちら

「Connectivity Restrictions (接続の制限)。これか!」更に読み進めると…。

・専用クロックピンからの入力は inclk[0], inclk[1]

・PLL からの出力クロックは inclk[2], inclk[3]

に入力しなければならないという制限がありました。

まさかそんな制限があるとは思っていなかったです。盲点でした。

( ここで注意事項!今回はあくまで Cyclone V®での話なのでデバイスによってはルールが違う可能性があります! )

そうです。私は PLL からのクロック出力を inclk[0 ], inclk[1] に入力していたのです!

さきほどのエラーの意味はそういうことだったのですね。

ということで、接続していた箇所を図 5 のように修正してみました。

修正後はコンパイルが無事に終わりました!

最終的に出来上がったのが図 6 の回路です。

この回路で無事にクロックの切り替えができ LED の点滅スピードを変える事が出来ました!

終わりに

IP は非常に便利ではありますが、使用する FPGA の種類によっては制限があるため

きちんとユーザガイドを読まないといけませんね。

皆様も IP を使用する際はご注意を!

しかし、使いこなせれば非常に便利ですよ!

・IP は単体で既に機能を有しているので回路設計の工数を大幅に削減することが出来る

・接続の制限などが存在しているので使用する際は必ずユーザガイドを参照する