はじめに

こんにちは!くらみぃです。

今回は C 言語奮闘記から少し外れ、Quartus® Prime の「RTL Viewer と Technology Map Viewer の使用用途の違い」について紹介したいと思います。

☆RTL Viewer

☆Technology Map Viewer

RTL Viewer

まず、 RTL Viewer という機能を紹介します。

この機能は Analysis & Elaboration 後に使用します。

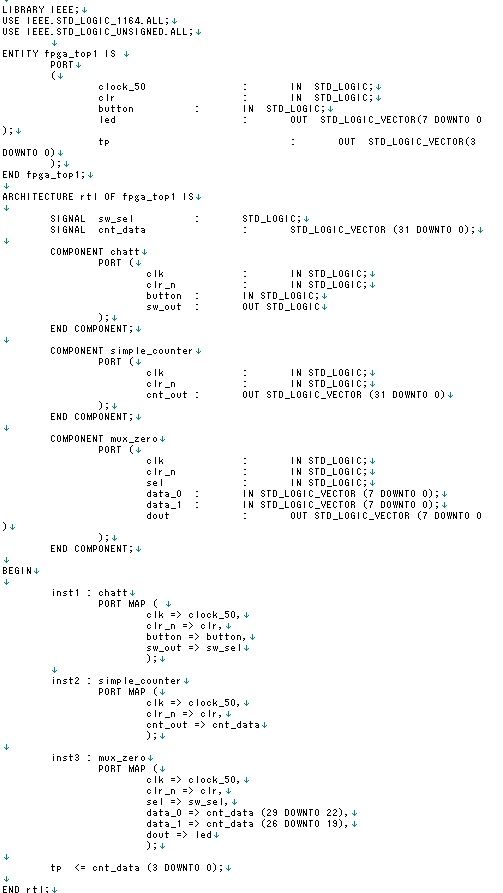

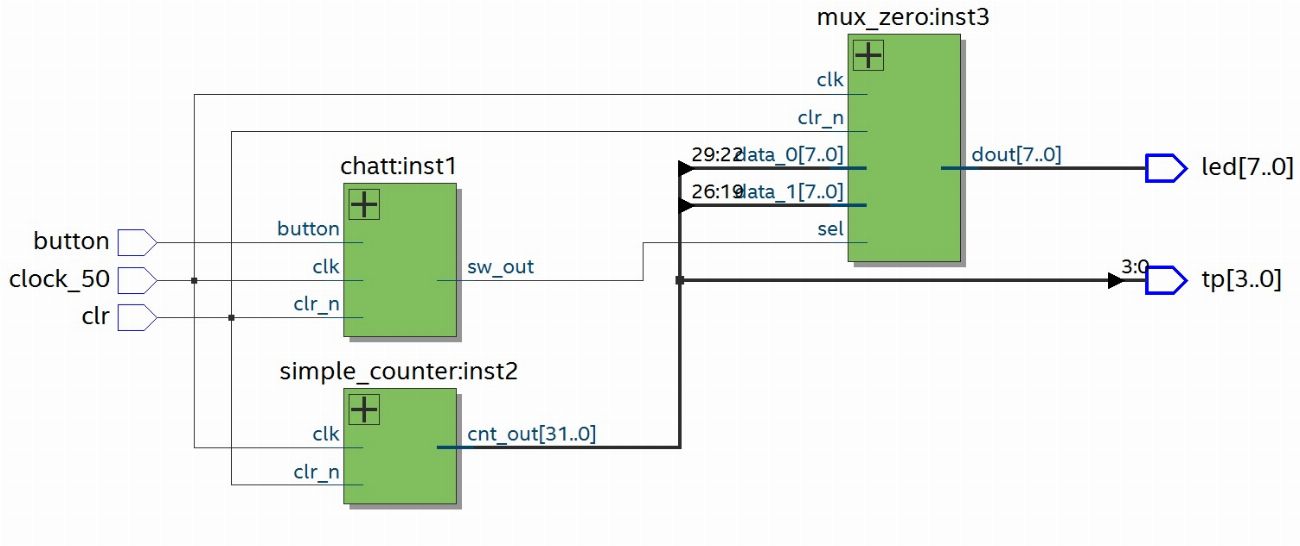

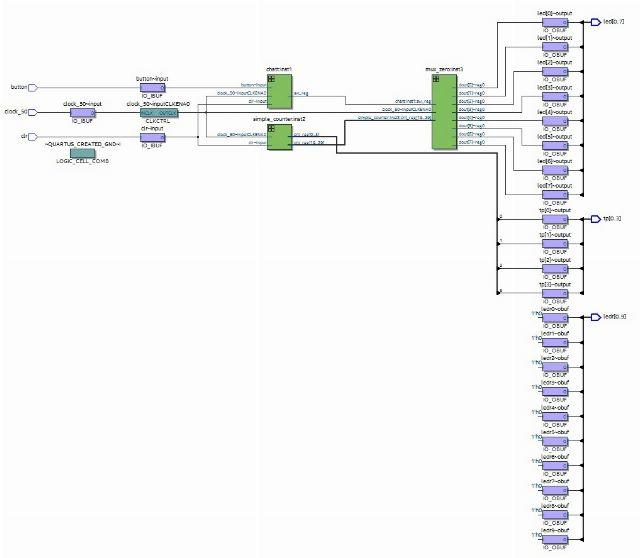

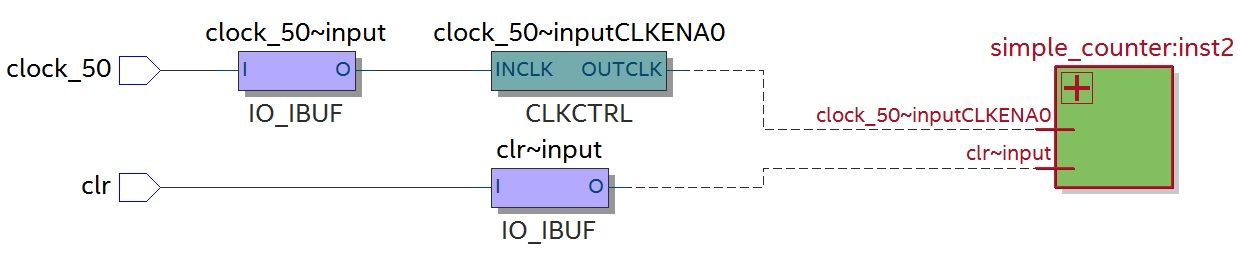

図1 が作成した HDL 回路の一例、図2 はこの回路を RTL Viewer で表示した回路の画面です。

緑色の箱は階層を表していて、+マークをクリックすると論理ブロックの内部を表示できます。

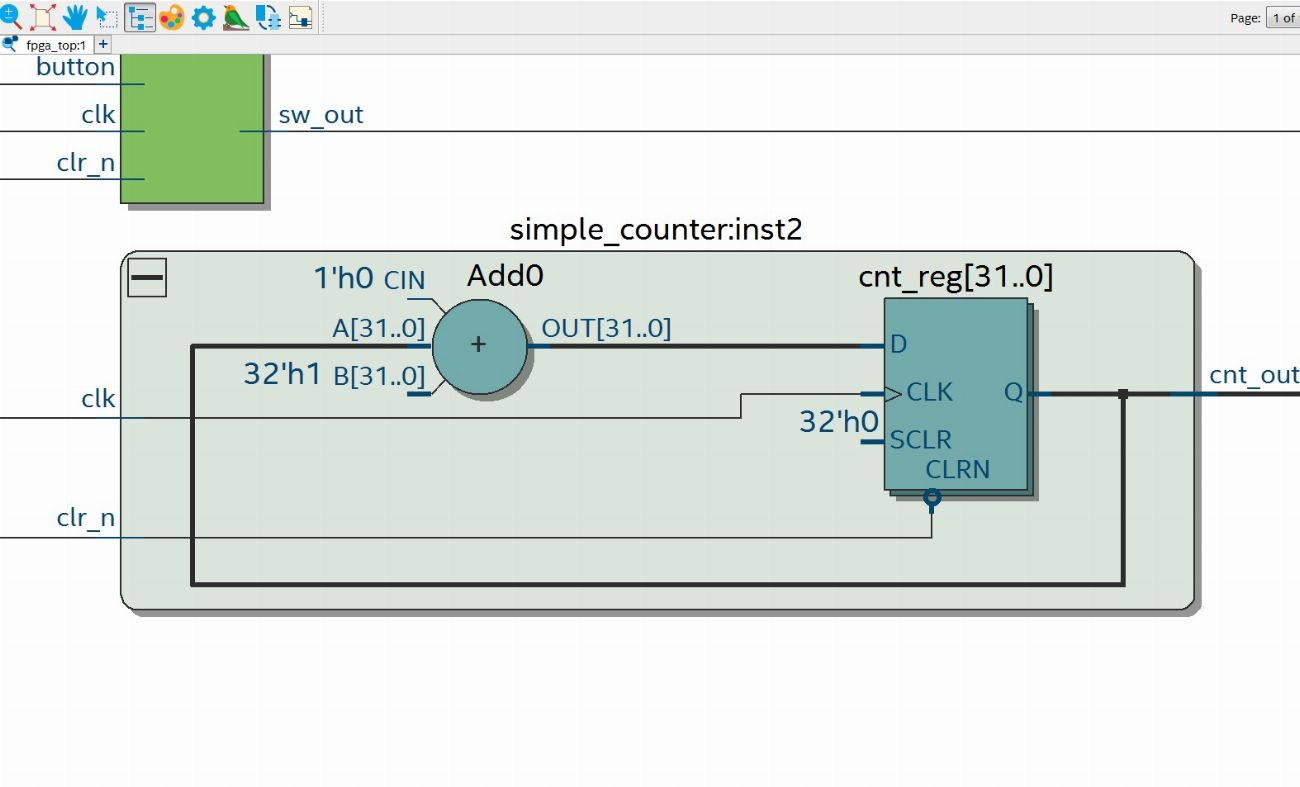

図 3 は図 2 のsimple_counter の+マークをクリックした後の図です。

RTL の構成要素は、I/O ピン、レジスタ、ゲート ( AND, OR, etc. ) 、演算子 ( adders, multipliers, etc. ) などです。

このように RTL Viewer を使用すると、作成したデザインを図式的に確認することが出来ます。

また、接続チェックや未接続ポートなどの最適化を考慮した状態で表示されるので、デバッグ時に使うこともできます。

私は製作実習で RTL Viewer を使うことで、接続したつもりになっていた未接続 I / O を見るけることができ、大変役に立ちました。

Technology Map Viewer

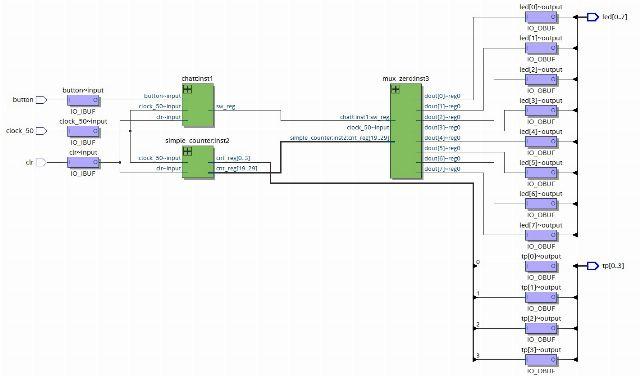

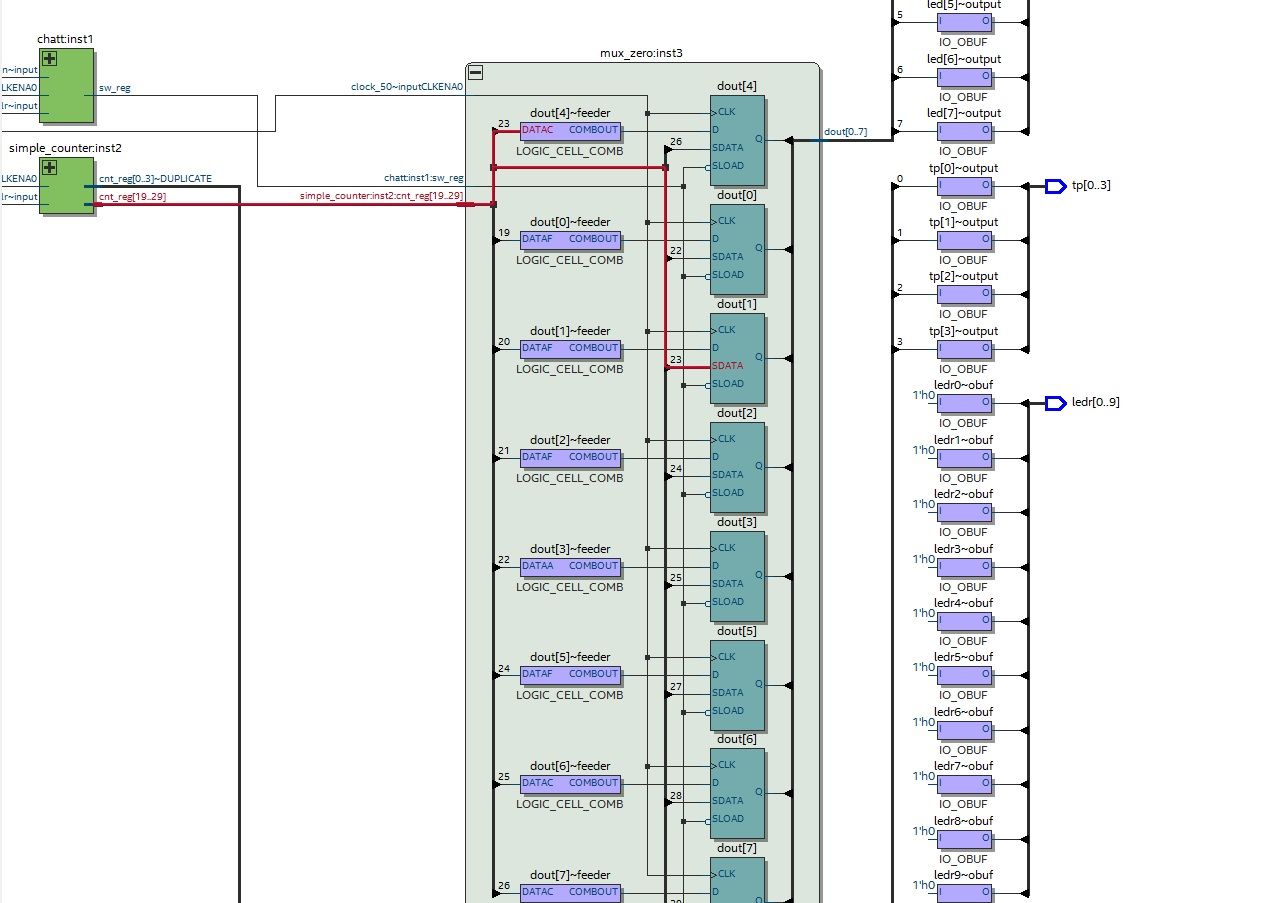

次に Technology Map Viewer 機能の紹介です。この Viewer を起動すると、論理合成および配置配線後の回路を図式的に確認することができます。(図 4, 5 )Technology Map Viewer には Post-Mapping と、 Post-Fitting があります。

【Post-Mapping】

論理合成後の回路をロジックエレメント、メモリブロック、I/O エレメント等のプリミティブに落とし込んだ状態で確認可能

【Post-Fitting】

配置配線後の回路で、配置配線時に実施された最適化も反映。

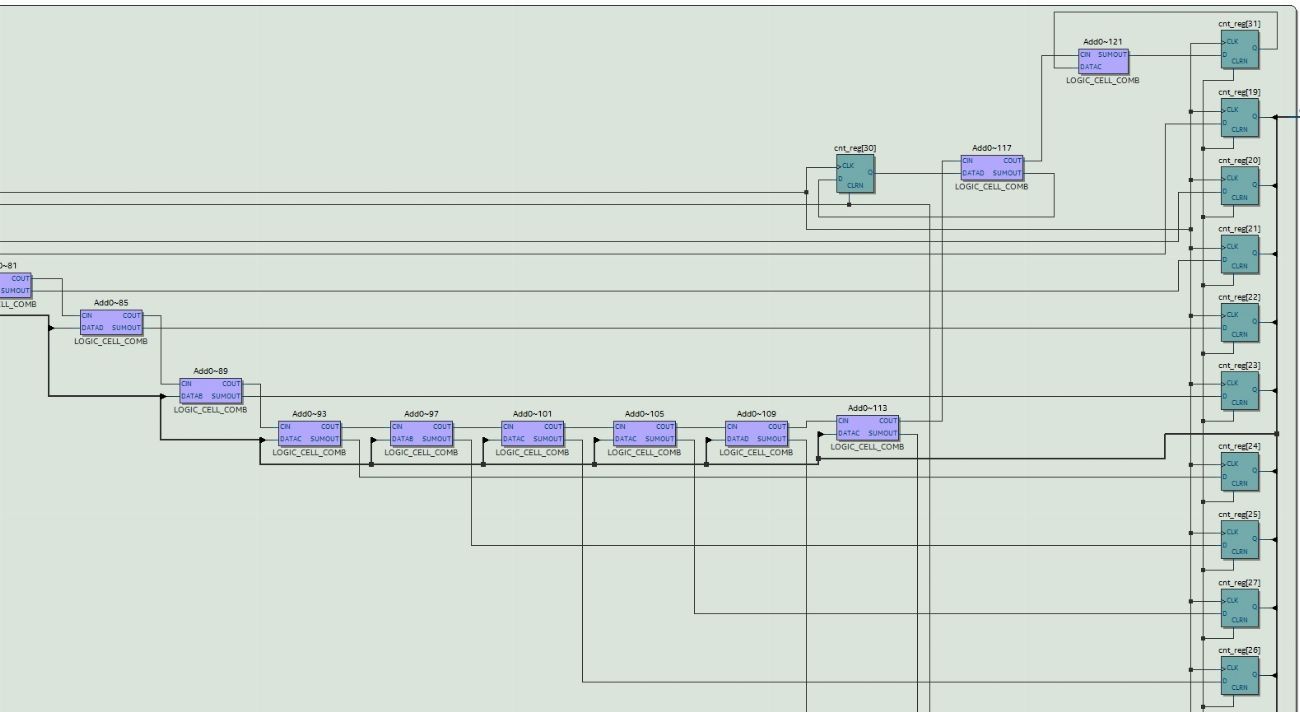

図 6 は simple_counter 階層の+マークをクリックして、論理ブロックの内部を表示させた図です。

青色の箱がロジックエレメントを表していて、緑色の箱がレジスタを表しています。

RTL Viewer では Add (加算器)として表示されていたものが、実際は図 6 のように構成されていたことがわかります。

Technology Map Viewer の構成要素は、I/O ピン、ロジックセル(LCells)、メモリブロックなどです。

Technology Map Viewer を使うと、自分の作ったデザインが Quartus® によって「 FPGA 内部のロジックセルをどう使って実現されたか」がわかります。

論理合成も配置配線も終わった最終的な結果を図式的に確認したい場合は、Post Fittingの Technology Map Viewer を使うと便利ですね。

<知っていると便利なこと>

1. RTL Viewer, Technology Map Viewer 共に、パスにカーソルを合わせて左クリックするとそのパスがハイライトされます。(図 7)

2. Filter を使用すると、選択した部分をピンポイントで確認することができます。

例えばsimple_counterをピンポイントで見たいときは、 simple_counter を右クリックして Filter を選択します。(図 8)

今回は Filter 機能の 1 つである Sources を選択しました。

これは、選択した入力に対してどんなパスが繋がっているかを確認できます。

まとめ

RTL Viewer と Technology Map Viewer の使用用途の違いは、以下のようになります。

◎RTL Viewer

デザインを図式的に確認したいとき。

◎Technology Map Viewer

FPGA 内部のロジックセルにマッピングされたデザインを図式的に確認したいとき。

上記 2 つの機能を使うと、デザインの確認やデバックをスムーズに行えて大変便利ですね!

次回記事も、ぜひご覧ください!!