インテル® の Cyclone® V SoC 開発キットは、インテルの低コストかつ低消費電力の Cyclone V FPGA ファブリックを利用した ARM® プロセッサ・ベースのカスタム SoC デザインを素早く開発するためのデザイン環境を提供します。このキットは、以下をはじめとするさまざまな機能をサポートしています。

- プロセッサおよびFPGA のプロトタイピングと消費電力測定

- 産業用ネットワーキング・プロトコル

- モーター制御アプリケーション*

- 画像/ビデオ処理アプリケーションのアクセラレーション*

- 最大転送レート 1,000 Mbps の PCI Express® (PCIe®) x4 レーン (エンドポイントまたはルートポート)

*各種 I/O およびインタフェース規格に対応した特定用途向けドータカードが別途用意されています。

注文情報

| 製品名 | Cyclone V SoC 開発キット |

| ご注文コード | DK-DEV-5CSXC6NES |

| Cyclone V SoC 開発キットには、5CSXFC6D6F31C8NES SoC が含まれています。 | |

開発キットの内容

Cyclone V SoC FPGA 開発キットには、以下のものが含まれています。

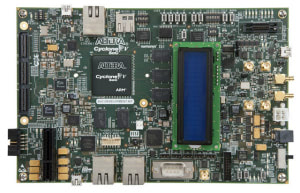

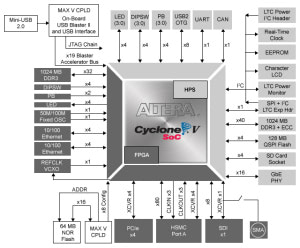

| Cyclone V SX 開発ボード | |||

| |

搭載デバイス: | ||

| Cyclone V SX SoC ̄5CSXFC6D6F31C8NES (SoC) | |||

| MAX® V CPLD ̄5M2210ZF256C4N (システム・コントローラ) | |||

| MAX II CPLD ̄EPM570GF100 (エンベデッド USB-Blaster™ II ケーブル) | |||

| FPGA コンフィギュレーション・ソース | |||

| エンベデッド USB-Blaster II (JTAG) ケーブル | |||

| EPCQ フラッシュ (PFL) | |||

| ハード・プロセッサ・システム (HPS) | |||

| FPGA メモリ | |||

| 1 GB の DDR3 SDRAM (32 ビット) | |||

| FPGA I/O インタフェース | |||

| 2 個の 10/100 イーサネット PHY (EtherCAT) | |||

| 1 個の PCIe Gen1 x4 メス・コネクタ | |||

| 汎用高速メザニン・カード (HSMC) ̄ 4 チャネルのトランシーバ、 | |||

| 16 チャネルの Tx LVDS、16 チャネルの Rx LVDS | |||

| 1 本の SDI チャネル | |||

| トランシーバ・チャネル 1 本あたり 4 個の SMA コネクタ | |||

| 4 個のプッシュ・ボタン | |||

| 2 個のスイッチ | |||

| 4 個の LED | |||

| HPS ブート・ソース | |||

| 128 メガバイトの QSPI フラッシュ | |||

| リムーバブル microSD カード・フラッシュ | |||

| FPGA | |||

| HPS メモリ | |||

| 誤り訂正コード (ECC) 対応 1 ギガバイトの DDR3 SDRAM (32 ビット) | |||

| 128 メガバイトの QSPI フラッシュ | |||

| microSD カード・ソケット (4 ギガバイトの microSD カード・フラッシュ・デバイスが付属) | |||

| HPS I/O インタフェース | |||

| 1 個の USB 2.0 On-the-Go (OTG) | |||

| 1 個の 10/100/1000 ギガビット・イーサネット (10GbE/100GbE/1000GbE) | |||

| 1 個の CAN | |||

| 1 個の UART (UART-USB ブリッジ) | |||

| 1 個のリアルタイムクロック (バッテリ・バックアップ付き) | |||

| 1 個のキャラクタ LCD (2 行) | |||

| 1/2 チャネルの 20 ビット・デルタシグマ・アナログ-デジタル・コンバータ (Linear Technology LTC2422) | |||

| 4 個のプッシュ・ボタン | |||

| 4 個のスイッチ | |||

| 4 個の LED | |||

| クロック | |||

| FPGA 基準クロック入力用プログラマブル・クロック・ジェネレータ (4 出力) | |||

| FPGA 基準クロック入力用 125 MHz LVDS オシレータ | |||

| FPGA 基準クロック入力用 148.5 MHz LVDS プログラマブル VCXO (電圧制御水晶発振器) | |||

| FPGA および MAX V FPGA クロック入力用 50 MHz シングルエンド・オシレータ | |||

| MAX V FPGA コンフィギュレーション・クロック入力用 100 MHz シングルエンド・オシレータ | |||

| HPS クロック用 SMA 入力 | |||

| 電源 | |||

| ラップトップ DC 電源入力アダプタ (14 ~ 20 V) | |||

| システム・モニタ回路 | |||

| 電源 (電圧、電流、ワット数) | |||

| HSMCブレークアウト・ボード | |||

| HSMC ループバック・ボード | |||

| 筐体 | |||

| ボード寸法 8.19” x 5.22” | |||

| Cyclone V GX FPGA 開発キット・ソフトウェアの内容(<関連資料>からダウンロード可能) | |||

| デザイン例 | |||

| ボード・テスト・システム (BTS)* | |||

| ボード・アップデート・ポータル・ウェブ・サーバーによるゴールデン・システム・リファレンス・デザイン | |||

| 関連資料(<関連資料>を参照) | |||

| SoC エンベデッド・デザイン・スイート・サブスクリプション・エディション | |||

| ARM Development Studio 5 (DS-5™) Altera Edition ツールキット | |||

| ハードウェア/ソフトウェア ハンド・オフ・ツール | |||

| アプリケーション開発用 Linux ランタイム・ソフトウェア | |||

| ファームウェア開発用 SoC ハードウェア・ライブラリ | |||

| アプリケーション例 | |||

| Quartus® II ソフトウェア・ウェブ・エディション v13.0 に対応した無償ソフトウェア | |||

関連資料

| ドキュメント | 説明 |

| Cyclone V SoC 開発ボードのセットアップおよび搭載されたソフトウェアの使用方法について解説しています。 | |

| ボードのコンポーネントおよびインタフェースに関する詳細を含んでいます。 | |

| キット・インストール (Windows)(FTP 経由) キット・インストール (Linux)(FTP 経由) |

リファレンス・マニュアル、ユーザー・ガイド、クイック・スタートガイド、部品表、レイアウト、PCB、回路図、ボード・アップデート・ポータル (BUP) のサンプル・ファイル、ボード・テスト・システム (BTS) のサンプル・ファイルなど、すべてのファイルのフル・インストール。BUP は、Qsys システム統合ツールを使用するようにアップグレードされています。 |

注: このキット・インストレーションは、Quartus II 開発ソフトウェア・ウェブ・エディション v13.0 で動作します。