~開発環境 Virtual Target も同時発表~

|

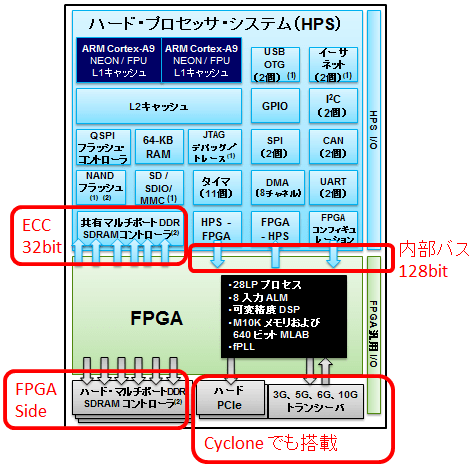

インテル®の新製品「SoC FPGA」は、デュアルコアARM® Cortex™-A9 MPCore™ プロセッサ、メモリ・コントローラ、および豊富なペリフェラル群からなるハード・プロセッサ・システム(HPS)と、28nm FPGA ファブリック(Cyclone® V ならびにArria® V)を統合したものです。プロセッサ・システムと FPGA 間の接続には、広帯域幅インタコネクトを使用しています。 |

SoC FPGA の特長

インテルが提供する SoC FPGA のシステム・アーキテクチャは以下の通りになっており、様々な特長があります。

| プロセッサ | ||

|

|

デュアルコア ARM Cortex-A9 MPCore プロセッサ | |

| 4,000 MIPS (コア当たり最大 800 MHz) | ||

|

|

倍精度 FPU 搭載 NEON™ コプロセッサ | |

| コア当たり 32 KB / 32 KB の L1 キャッシュ | ||

|

|

512 KB の共有 L2 キャッシュ | |

| マルチポート SDRAM コントローラ | ||

|

|

最大 533 MHz の DDR3 および LPDDR2 | |

|

|

最大 400 MHz の DDR2 | |

|

|

最大 200 MHz の Mobile DDR | |

|

|

統合 ECC サポート | |

| 広帯域幅オンチップ・インタフェース | ||

|

|

100 Gbps を超える HPS-FPGA インタフェース | |

|

|

100 Gbps を超える FPGA-SDRAM インタフェース | |

| コストと消費電力に最適化された FPGA ファブリック | ||

|

|

最も低消費電力のトランシーバ | |

|

|

最大 1,600 GMACS、300 GFLOPS | |

|

|

最大 25 Mビットの内蔵 RAM | |

|

|

ハード IP(Intellectual Property)を増加: PCIe® およびメモリ・コントローラ | |

| 柔軟なコンフィギュレーション | ||

| 豊富な開発環境 | ||

SoC FPGA でデザインする 5 つの理由

| ボード・サイズの削減 | |

|

FPGA、マイクロプロセッサ、および DSP ファンクションをシングル・チップに統合することでボード上のデバイス数を削減し、ボード・サイズや複雑さを最小限に抑えることが可能 |

|

| 消費電力の削減 | |

|

SoC FPGA を利用すれば、インテルに最適化された 28nm Low-Power ( 28LP ) プロセス・テクノロジ、豊富なハード IP 群、および低消費電力シリアル・トランシーバを活用可能 |

|

| トータル・システム・コストの削減 | |

|

必要なディスクリート・デバイス、電源レール、およびオシレータの数が少なくてすむため、部品 ( BOM ) コストの削減を実現 |

|

| FPGA の柔軟性を活用したデザイン | |

|

インテルおよびサードパーティ IP パートナーの広範なソフト IP コアから最適なものを選択して、カスタム ARM プロセッサ・システムを素早く構築することが可能。また、柔軟な FPGA ファブリックによって業界規格や市場の要求の変化に対応。さらに、Quartus® II 開発ソフトウェアと Qsys システム統合ツールを使用して、カスタム・ハードウェア・デザインを素早く開発可能 |

|

| 共通の開発ツール | |

|

ARM のソフトウェア開発ツール、オペレーティング・システム、およびミドルウェアの強力なエコシステムを活用可能。 |

28nm FPGA ポートフォリオをさらに拡充

インテルは、多様なデザイン要件に合わせて完全な 28nm デバイス・ポートフォリオを提供しています。

SoC FPGA は、広範な Cyclone V SoC FPGA および Arria V SoC FPGA ファミリをさらに拡充します。各デバイス・ファミリは、性能、I/O リソース、パッケージ・サイズ、消費電力、コストなどの要件への最適化により、パートナンバーごとに差別化が図られています。

ソフトウェア開発を今すぐ開始

SoC FPGA ハード・プロセッサ・システム、およびボード・レベル・コンポーネントの高速機能シミュレータであるインテル SoC FPGA Virtual Target (バーチャル・ターゲット)を使用すれば、SoC FPGA 用のアプリケーション・ソフトウェアの開発を今すぐ開始できます。SoC FPGA Virtual Target は、ソフトウェアに対して卓越した制御性と可視性を提供し、複雑なマルチコア・プロセッサ・ベースの組込みシステムにおいて、一層強力なデバッグ能力を実現します。

SoC FPGA の詳細情報

| ブローシャ: 「インテルの ARM ベース SoC FPGA」(PDF) | ||

| ホワイトペーパー: | ||

| 「次世代組込みシステム向け、カスタマイズ可能な ARM ベース SoC FPGA」 (PDF) | ||

| Advance Information Briefs: | ||

| o | SoC FPGA product overview (英語版・PDF) | |

| o | ARM Cortex-A9 processor (英語版・PDF) | |

| ※上記 「Advance Information Briefs」 の日本語版をご希望の方はご連絡ください。日本語化が完了次第、お送りいたします。 | ||

| Cyclone V FPGA ファミリ | ||

| Arria V FPGA ファミリ | ||

| ARM Cortex-A9 プロセッサ | ||