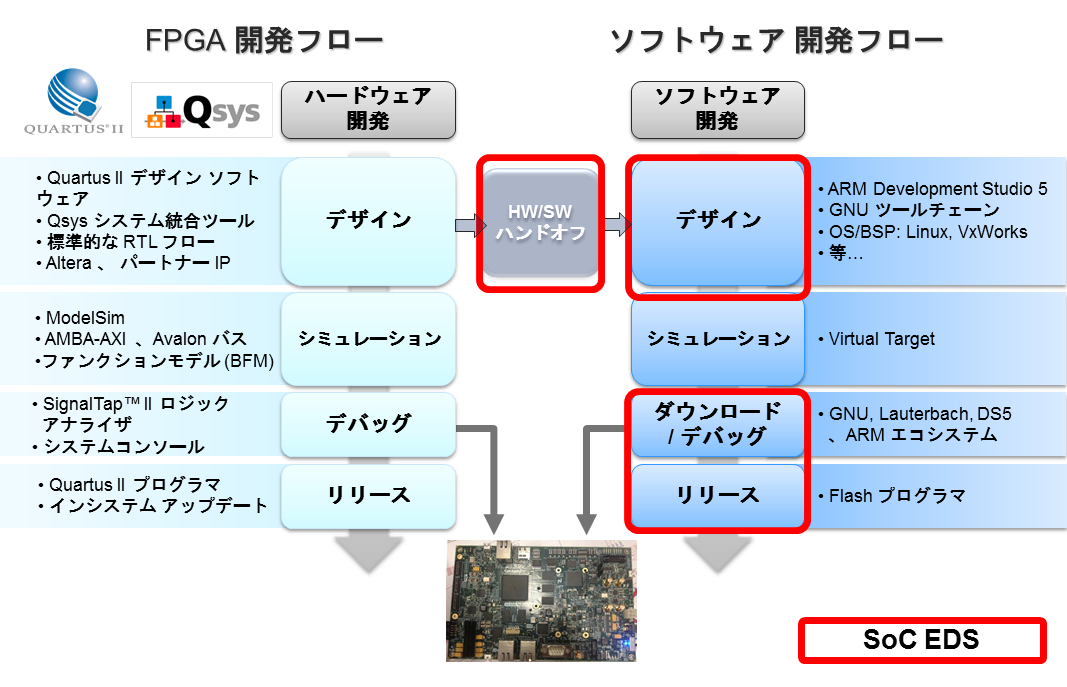

インテル® SoC エンベデッド・デザイン・スイート (EDS) は、インテル SoC ハードウェア・プラットフォーム上でファームウェア およびアプリケーション・ソフトウェアを開発できるようにする以下の開発ツール群を提供します。

インテル SoC EDS が提供する開発ツール群

|

|

|

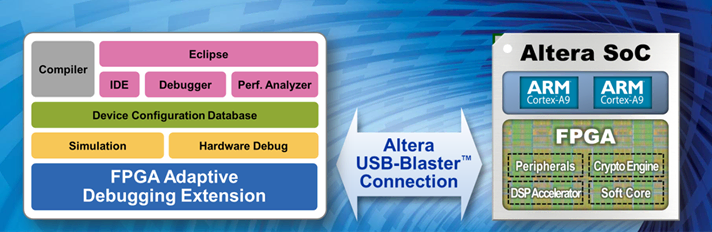

業界初の FPGA 適応型ソフトウェア・ツールキット: ARM Development Studio 5 (DS-5) Altera Edition

ARM DS-5 Altera Edition ツールキットは、インテル SoC Embedded Design Suite (EDS) の一部として、インテルとの独占契約によって提供されます。

このツールキットは、システム開発に対応できる ARM DS-5 ツール・スイートをインテル SoC デバイスと組み合わせることで、チップ全体の比類ないレベルの可視化とコントロールを、エンベデッド開発者にもたらします。

DS-5 Altera Edition の特長

| 非介入型トレース |

ハードウェア / ソフトウェアのハンドオフ

インテルのハードウェア/ソフトウェア間インタフェース・ユーティリティは、ハードウェアおよびソフトウェア・チームが独立して作業し、それぞれが使い慣れたデザイン・フローを使用できるようにします。

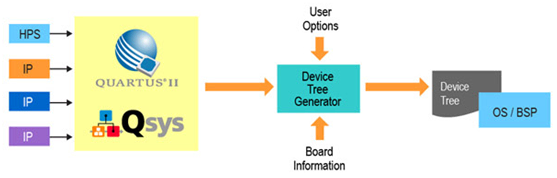

これらのユーティリティは、Quartus® II 出力ファイルからソフトウェア・デザイン・フロー用インタフェース・ファイルを生成します。あるユーティリティ・プログラムはデバイス・ツリーを生成します。

デバイス・ツリーは、オペレーティング・システム (主に Linux) に対してハードウェアを記述する業界標準の方法です。

カーネル起動時に対応するドライバがロードするように、ボードおよび FPGA の構成に対応するハードウェアを規定します。