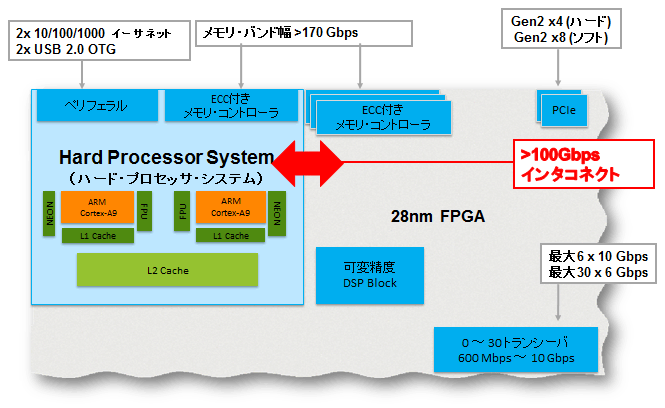

高いバンド幅を実現するインタコネクト

HPS と FPGA ファブリック間の高スループット・データ・パスは、2 チップ・ソリューションでは実現不可能なレベルのインタコネクト性能を提供します。

HPS と FPGA ファブリックの緊密な統合により、プロセッサと FPGA 間の統合データ・コヒーレンシを維持しつつ、100Gbps を超えるピーク帯域幅を実現します。さらに、プロセッサと FPGA の間から 外部 I/O パスを排除したことで、システム消費電力の大幅な削減にも貢献します。

<優れたデータ・インテグリティと広帯域バンド幅>

広帯域幅 HPS-to-FPGA インタコネクト・バックボーン

HPS (Hard Processor System) と FPGA は独立して動作可能ですが、高性能 ARM AXI バス・ブリッジによる広帯域幅システム・インタコネクトを介して緊密に結合されています。FPGA ファブリック内の IP バス・マスタは、FPGA-to-HPS インタコネクトを介して HPS バス・スレーブにアクセスできます。同様に、HPS バス・マスタは、HPS-to-FPGA ブリッジを介して FPGA ファブリック内のバス・スレーブにアクセスできます。いずれのブリッジも ARM AXI-3 準拠であり、同時リード/ライト・トランザクションをサポートしています。追加された 32 ビット軽量 HPS-to-FPGA ブリッジは、HPS と FPGA ファブリック内のペリフェラルの間に低レイテンシのインタフェースを提供します。また、最大 6 個の FPGA マスタが HPS SDRAM コントローラを共有できることに加え、ARM プロセッサを使用して専用 32 ビット・コンフィギュレーション・ポートを介してプログラム制御下の FPGA ファブリックをコンフィギュレーションすることも可能です。

| HPS-to-FPGA | |

| 広帯域幅に最適化された、コンフィギュレーション可能な 32/64/128 ビット AMBA AXI インタフェース | |

| FPGA-to-HPS | |

| 広帯域幅に最適化された、コンフィギュレーション可能な 32/64/128 ビット AMBA AXI インタフェース | |

| 軽量 HPS-to-FPGA | |

| 低レイテンシに最適化された 32 ビット AMBA AXI インタフェース | |

| FPGA-to-HPS SDRAM コントローラ | |

| 6 個のコマンド・ポート、4 個の 64 ビット・リード・データ・ポート、および 4 個の 64 ビット・ライト・データ・ポートを持つ、コンフィギュレーション可能なマルチポート・インタフェース | |

| 32 ビット FPGA コンフィギュレーション・マネージャ |