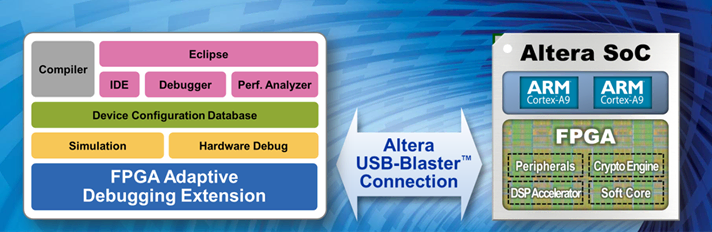

Arm® Development Studio 5 (以後 DS-5) の高度なマルチコア・デバッグ機能と、FPGA エリアへの対応および インテル® FPGA の Signal Tap ロジック・アナライザーとのシームレスなリンクによる従来にないレベルのデバッグを実現するのが、インテル SoC FPGA エンベデッド開発スイート (SoC EDS) に含まれる DS-5 インテル SoC FPGA エディション・ツールキットです。

DS-5 インテル SoC FPGA エディション・ツールキット

・CPU と FPGA 間のデバッグ障壁を取り除きます

・USB-Blaster II 単体でソフトウェアとハードウェアのデバッグ環境に接続

・Signal Tap ロジック・アナライザーと連動して、CPU ドメインと FPGA ドメインの間に高度なシグナルレベルの

ハードウェア・クロス・トリガを提供

・Cortex-A9 コアおよび FPGA 上で合成される CoreSight 対応 IP コアの同時デバッグならびにトレース

生産性を向上させる DS-5 インテル SoC FPGA エディションの機能

・USB-Blaster II 単体でソフトウェアとハードウェアのデバッグ環境に接続

・FPGA ペリフェラルのレジスタ・ビューを自動作成

・CPU のインストラクションを妨げず、アプリケーション・イベントと

FPGA ハードウェア・イベントを互いに関連付け可能

・CPU と FPGA 間のハードウェア・クロス・トリガ

・Cortex-A9 コア および FPGA 上で合成される CoreSight 対応 IP コア

の同時デバッグならびにトレース

・Streamline に対応: ソフトウェア負荷および CPU と FPGA にわたる

バス・トラフィックの統計解析

生産性を向上させる DS-5 インテル SoC FPGA エディションの機能

・業界最先進の ARM 向けマルチコア・デバッガ

・JTAG ベースのシステム・レベル・デバッギングと、gdbserver ベースの

アプリケーション・デバッギングをワンパッケージ化

・Linux ベースのアプリケーション開発を可能にする Yocto プラグイン

・統合された OS にあわせた解析ならびにデバッグ機能

FPGA 適応型、統合された表示

・あらかじめ設定済みの CPU サブシステム・ペリフェラル・

レジスタ・ビュー

・FPGA 内ペリフェラル・レジスタ・ビューの自動生成

・ペリフェラル・レジスタ・ビュー

- 定評のある DS-5 インタフェース

- 自動生成

- ビット・フィールドによってグループ化

- リストからオプションを選択

FPGA 適応型、統合デバッグ

・インテル SoC FPGA デバイスは、信号イベントの非侵入キャプチャ

と可視化のために、FPGA ファブリックにARMデバッグとトレース

バスを接続します

・DS-5 は CPU コアとコンパチブル IP に対する同時デバッグと

トレース接続をサポート

・DS-5 は、ソフトウェア・イベントと CPU 命令トレースでトリガ

とタイムスタンプを使用することで、FPGA 信号イベントの関連

付け可能

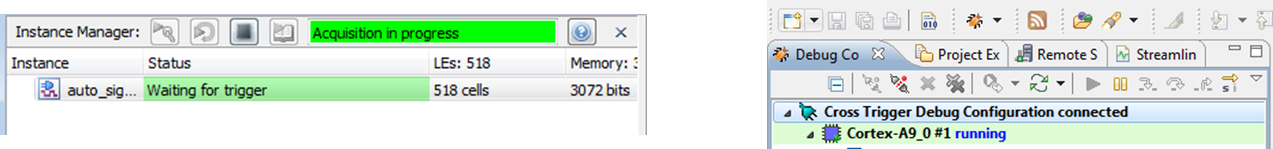

クロス・トリガ

・ CPU ドメインと FPGA ドメイン間の高度な信号レベル・ハードウェア・

クロス・トリガ

・クロスドメインのハードウェア/ソフトウェア協調デバッグを可能に

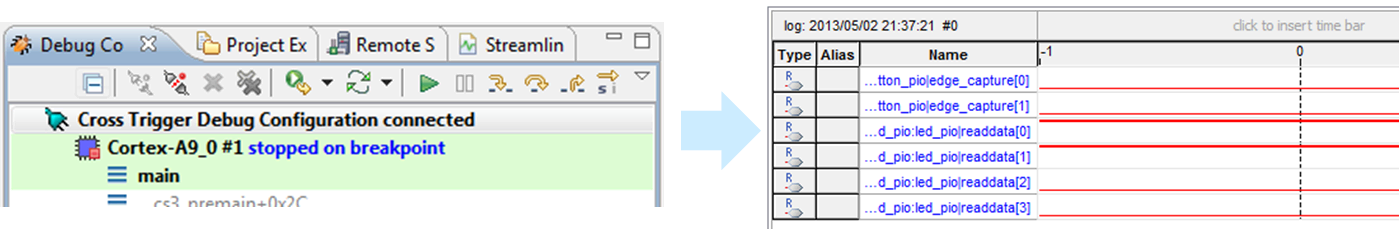

デバッガと Signal Tap の実行

・Signap Tap ロジック・アナライザーとデバッガーを起動

・ARM 内蔵ハードプロセッサシステム (HPS) ⇒ FPGA クロス・トリガ

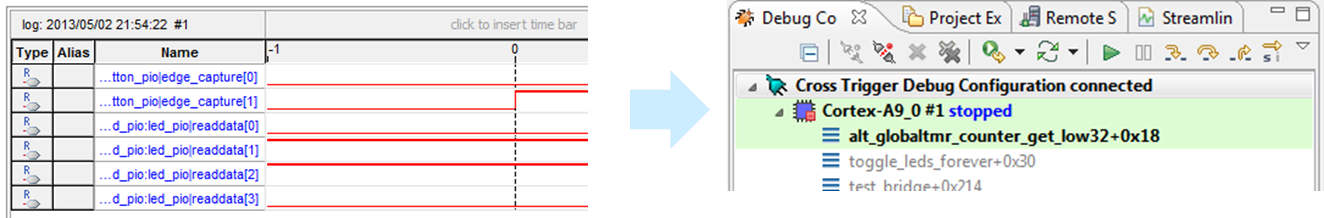

・FPGA ⇒ ARM 内蔵ハードプロセッサシステム (HPS) クロス・トリガ

HW と SW のイベントの関連付け

・Signal Tap ロジック・アナライザーからのトリガ・ポイントを

設定します

・設計者は、キャプチャしたトレースとタイムスタンプ相関イベント

を分析することができます

FPGA クロス・トリガ・インタフェース

・標準の ARM CoreSight デバッグ・コンポーネント

・FPGA と MPU 間のクロス・トリガをデバッグします

- 8トリガ入力 + 8 ACK 信号

- 8トリガ出力 + 8 ACK 信号

・FPGA のクロック・ソースで実行される

・トリガは同期される

・トリガ・ハンドシェイク・オプションがサポートされている

- FPGA へのトリガ出力は、ACK 信号が FPGA から受信される

までアサートされる

・CTI はクロス・トリガ・マトリクス・ユニットに接続されている

- インフラストラクチャをデバッグするためにトリガ接続を構成

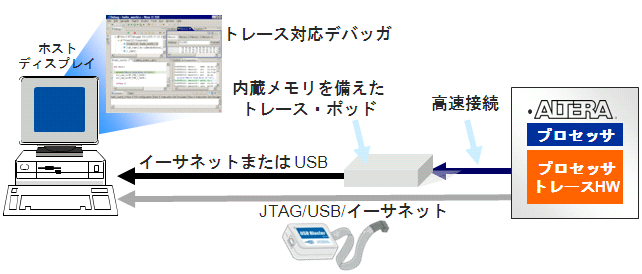

リアルタイム・トレース

・プロセッサ ‘データ・ロガー’ システム

・フルスピードで動作し、リアルタイム・ソフトウェアの問題をデバッグ

・ハードウェアは、事前に定義された条件でトリガ

- アドレス値、データ値、またはそれらの組み合わせ

・デバッガでの分析のために、オンチップまたはオフチップ・メモリへ、命令またはデータ・フロー情報を保存

インテル SoC の包括的な開発環境

インテル SoC FPGA エンベデッド開発スイート (SoC EDS) に含まれる DS-5 インテル SoC FPGA エディション・ツールキットにより、ARM DS-5 の高度なマルチコア・デバッグ機能と FPGA エリアへの対応およびインテルの Signal Tap ロジック・アナライザーとのシームレスなリンクによる、従来にないレベルのインテル SoC 全体の可視化と柔軟性を実現します。