インテル®社のFPGA は内部の SRAMメモリ にコンフィギュレーション・データを格納して動作します。しかし、SRAMは揮発性なのでFPGAの電源を落とすと、FPGA内部のコンフィギュレーション・データは消えてしまいます。

そこで、FPGAとは別に不揮発性のメモリをコンフィギュレーション・デバイスとして用意するか、ダウンロード・ケーブルなどからコンフィギュレーション・データを読み込む必要があります。

特徴

インテル社のシリアル・コンフィギュレーション・デバイスは、業界で最も使いやすいコンフィギュレーション・デバイスです。

シリアル・コンフィギュレーション・デバイスは、ISP(イン・システム・プログラマビリティ)機能と再プログラミング機能を持っているだけでなく、シリアル・フラッシュ製品よりも長い製品寿命を実現しますので、実装するシステムの製品寿命に対応するコンフィギュレーション・デバイスとしての柔軟性を提供します。

シリアル・コンフィギュレーション・デバイスには、以下のような機能を備えています。

|

生成されたコンフィギュレーション・データは、Quartus II ソフトウェアにより約半分以下に効率よく圧縮されます。図 1 に示されているように、圧縮されたデータは次にコンフィギュレーション・デバイスにダウンロードされ、そこで伸張エンジンによって復元されてからプログラマブル・ロジック・デバイス(PLD)に送られます。 |

|

図1 |

|

システムのダウンタイムを必要最小限に抑え、デザインをイン・システムで迅速に更新できることが求められています。このニーズに応えるのが、インテルのエンハンスド・コンフィギュレーション・デバイスのページ・モード機能です。この機能により、サイズが動的に変わるページを最大 8 ページまで保存することが可能になります。このページ・モード機能を使用して、図 2 に示されているように、1 個のコンフィギュレーション・デバイスに同じ PLD 用のコンフィギュレーションを複数保存しておけば、ページ・モード・ピンをアサートするだけでその PLD の機能を動的に切り換えることができるようになります。 |

|

図2 |

|

エンハンスド・コンフィギュレーション・デバイスでは、3 種類の方法で PLD をプログラミングすることができます。従来のシリアル・モード、最大 8 個の PLD を並列にプログラミングすることができる複数コンフィギュレーション・モード、それに新しい高速 8 ビット・パラレル・モードです。 |

|

インテルのシリアル・コンフィギュレーション・デバイスは、最大 64M ビットの フラッシュ・メモリを搭載しています。 フラッシュ・ メモリの未使用領域は、汎用メモリとして利用可能です。この汎用メモリに、Nios® または Nios II エンベデッド・プロセッサ を使用してアクセスすることができるため、シリアル・コンフィギュレーション・デバイスは フラッシュ・ メモリとコンフィギュレーション・デバイスを組み合わせた完全なソリューションになります 。 |

図3 |

|

このメモリはエンベデッド・プロセッサのブート・ローダ・プログラム用 ROM としても使用でき、これにより必要な基板スペースが削減され、オンボード・メモリ・モジュールの追加が不要になり、最終的にはシステム全体のコストを削減できます。 |

|

JTAG インタフェースを使用したISP(イン・システム・プログラマビリティ)機能に対応しますので、JTAG経由で簡単にコンフィギュレーションすることが可能です。 |

|

図4 |

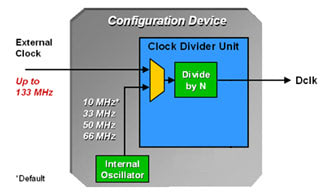

| エンハンスド・コンフィギュレーション・デバイスではプログラマブル・クロック機能により複数のクロック速度を選択できるため、デザインの柔軟性が向上するとともにコンフィギュレーション時間が短縮されます。図 6 に示されているように、内部で生成される 4 種類のクロック(10MHz、33MHz、50MHz、66MHz)から選択するか、最大 133MHz の外部クロックを使用することができます。Quartus II ソフトウェアを用いてクロック分周器の係数 N と M を調節すれば、所望の任意の周波数のクロックに変更することができます。このプロセスは通常は、所望の周波数にソフトウェアで設定するのと同じくらい簡単です。 |

|

図5 |

| デザインの総コストを考える上で重要な点は、基板面積です。 ソリューションのコストは、そのソリューションが消費する基板面積が増えるほど高まります。 インテルのシリアル・コンフィギュレーション・デバイスは、 8 ピンおよび 16 ピン SOIC パッケージに封止されています。 8 ピン・パッケージが占める基板面積は、30 mm2 以下のため、1 つの SOPC ソリューション全体に要する基板面積は最も小さく抑えられます。全てのシリアル・コンフィギュレーション・デバイスが同一パッケージを使用しているため、置き換えが簡単です。 |

|

図6 |

コンフィギュレーションデバイスの種類

コンフィギュレーションデバイスの種類

EPCS(シリアル・コンフィギュレーション・デバイス)

1M ビットから128Mビットで構成され、最新のコンフィギュレーション手法をサポートするコンフィギュレーション・デバイスです。

EPCQ

128M ビットと256Mビットで構成され、大規模FPGA用のコンフィギュレーション・デバイスです。

Active Serial(AS)モードの4倍速をサポートしています。

EPC(エンハンスド・コンフィギュレーション・デバイス)

主に旧FPGA製品のコンフィギュレーションに使用するコンフィギュレーション・デバイスです。

4Mビットから16Mビットで構成されます。