どうも。

試行錯誤をしながらも、製作実習の ステップ 2. ハードウェア設計に移った 無知無知くん です。

今回は 第二弾!Verilog HDL でハードウェアを設計するお話です。

![]()

※ 前回の<仕様書・基板作成編>は、こちらよりご覧ください。

目次

・Verilog HDL 記述 (7セグメント LED 時計、ドットマトリクス LED)

・次回予告

Verilog HDL 記述

半田づけと同じくらいイイ感じに距離を取っていたハードウェア言語。

さすがに観念して、Verilog HDL で 7セグメント LED 時計 (以下 7seg 時計) を設計します。

7seg 時計

時計を作るためには、外部から入力した 50MHz のクロック周波数を使って、FPGA で "1 秒間隔のパルス信号" を作る必要がありました。

まずは、Cyclone® 10 LP 評価キットの基板に搭載されているクロック周波数 50 MHz で動作するアップカウンターを作りました。

これで 50,000,000 を数えたら そこで 1 秒間。

そのカウンターをリセットさせ、同時にクロック 1 周期分のパルスを生成させました。

このパルス信号を、秒用のカウンターのクロックイネーブル信号に用いれば、

1 秒で動作するカウンターのできあがり!

続いて、時・分・秒 に それぞれに 1桁目用と2桁目用のカウンターを用意。

秒 と 分 のカウンターは、この2桁が 60 になるタイミングで、クロック 1 周期分のパルスを生成させ

下図のように 分、時 それぞれのカウンターのクロックイネーブルに使いました。

あとは、プッシュボタンが押されているか否かで、時 & 分 / 秒 のどちらを 7seg に表示するか選択させました。

ドットマトリクス LED

7seg 時計を Verilg HDL で記述した際に採用したダイナミック点灯を応用し、カウンターを使って 50000ns 経過する間に

1つのドットマトリクス LED 上のすべての LED に対して、点灯・消灯を制御する記述をしました。

こうすれば、人間の目には点灯している箇所が、同時に点いたように見えるんです!

表情を変化させる

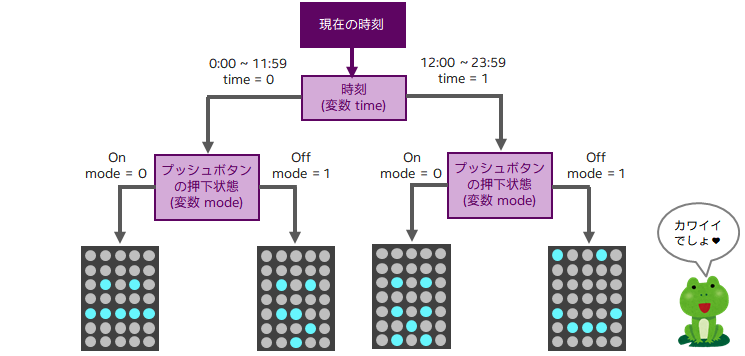

7seg 時計の時刻と、プッシュボタンの押下状態によって点灯パターンを変えるため、2つの変数を用いました。

2つの変数の組み合わせにより、4パターンの表情を作ることができました。

そんなこんなで、ステップ 2 の課題を終えました。

振り返ってみると...

知らなくてヤバかったこと

知らヤバ 1. デコーダーって何?

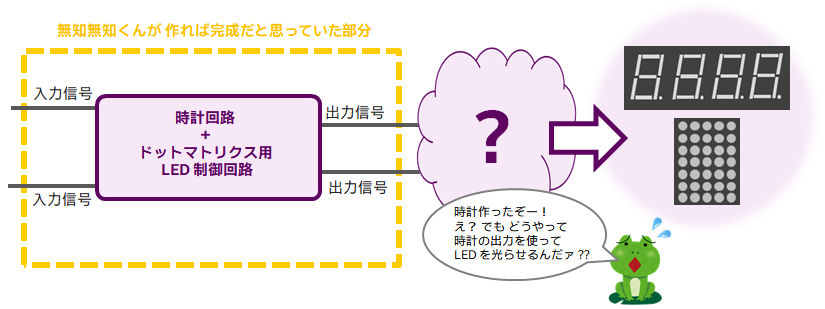

前回の #1 <仕様書・基板作成編> で「まぁ いけるっしょ(笑)」と思ったのは、下図の点線枠内を作れば完成だと思った 勘違いのせいでした。

時計回路を Verilog HDL で仕上げ、"ヨシ!強敵を倒した!" と思いきや

その出力信号をピンアサインしようと考えたときに … あれ?どうつなげれば良いんだろう?

その後段で何をすれば LED を点灯・消灯させられるのか、無知無知くんには 謎 でした。

先輩たち相談すると、"デコーダー" という用語が。

その後 自分で調べて、その処理がナニモノかを知ったときには 「マジかよ!そういうことかーーーッ!!!」 と声に出てしまいました。

そんな強大なアイテムがあったとは。そして、それを知らなかったオレ。

そのときは もう 自分に対して絶望しかありませんでした Ozn

知らヤバ 2. ダイナミック点灯 & case 文の使い方

前回の#1 <仕様書・基板作成編>で、7セグメント LED の使い方はダイナミック点灯で

動作させることがわかりましたが、実際にそのやり方までは全く分かっていませんでした。

グー〇ル先生や先輩たちに聞いて、どうにかこうにか辿り着いた結論が こんな感じです。

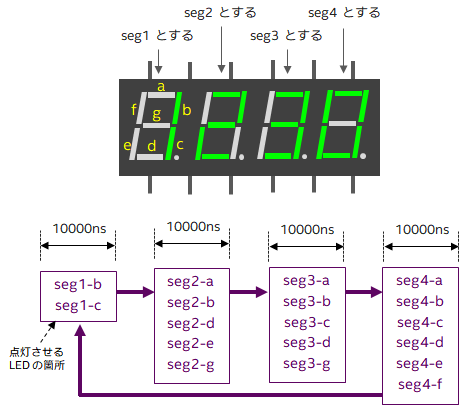

例えば 1230 と表示させる場合は、下図のとおりに各 LED を点灯させなければなりません。

でも 4桁の 7seg LED のピン仕様は各 LED との接続が 1対1 ではないので、同時に点灯させられません。そこで、各桁の 7seg LED を ある一定の時間だけ 順次点灯させる方法にしました。

グー〇ル先生で調べてみると

人間が目で追える点滅の速さは 50ms ~ 100ms くらいだそうなので

点灯時間を 10000ns に決めました。

具体的には

1ns 周期で 40000 回カウントアップするカウンター(cnt) を作成し、

case 文を使って以下のように制御しました。

0 ns ~ 9999 ns で seg1 が点灯

10000 ns ~ 19999 ns で seg2 が点灯

20000 ns ~ 29999 ns で seg3 が点灯

30000 ns ~ 39999 ns で seg4 が点灯

[10000ns 間隔は速すぎて人間の目には追えない = 同時に点灯しているように見える] ということだったんですね!

これで、無事にダイナミック点灯ができました。

こうしときゃぁ良かったなポイント

ハードウェア設計 (ステップ 2) で「こうしときゃ良かった」と実感したことが、いくつかありました。

![]() 自分が考えたデザイン (デジタル論理回路) の全体構造を 理解しておけば良かった

自分が考えたデザイン (デジタル論理回路) の全体構造を 理解しておけば良かった

… 仕様書の内容をもっとしっかりと書いておけば良かったと 猛反省

![]() Verilog HDL 記述で自分の回路をいきなり記述する前に、

Verilog HDL 記述で自分の回路をいきなり記述する前に、

新人研修中の言語講座で出された課題の演習を 改めてやっておけば良かった

次回予告

ステップ 1 の終盤で調子に乗ったら ステップ 2 で即ヘシ折られ、慎重派になった無知無知くん。

「もう 同じ過ちはしないぞ!」

次回、ソフトウェア設計編 (feat. Nios® II) です。