はじめに

こんにちは。最近少しずつですが成長を感じてきたなみぃです。

今回は最新デバイスである Stratix® 10 FPGA の 新機能の紹介です。

Stratix 10 にはデザイン全体のパフォーマンスを向上できる注目の新機能がたくさんあります!

今回から数回にわたって紹介予定ですので、皆さんぜひチェックしてください。

Hyper-xx との出会い

=ある日の会議にて=

課長「Stratix 10 のHyperFlexTM に関して……。Hyper-Register が追加されたことにより Hyper-Retiming が……。」

私「(……Hyper ? ) 」

課長「Hyper-Pipelining が………。」

私「…………………」

課長「Hyper-Optimization が…………。」

私「(Hyper- 何とかは一体いくつあるんだ…) 」

Hyper-xx 多いですね…。

そうして、それぞれの区別が付かないまま会議が終了してしまいました。

これはまずいと思い、席に戻って早速調べてみました。

ちなみに、私が認識している Hyper-xx は

・HyperFlex

・Hyper-Register

・Hyper-Retiming

・Hyper-Pipelining

・Hyper-Optimization

の 5 種類。それぞれ何を表すのか見ていきましょう。

HyperFlex とは?

HyperFlex とは FPGA のパフォーマンスを向上させるための仕組み全体のことです。

これは Stratix 10 から追加された仕組みです。

そして実際にパフォーマンスを上げる機能が上記の

・Hyper-Retiming

・Hyper-Pipelining

・Hyper-Optimization

などです。

なぜこれらの新機能が Stratix 10 から使用できるようになったのでしょうか?

そう。それは、新しく追加されたレジスタのおかげです!

それが Hyper-Register です!

Hyper-Register とは?

Hyper-Register とは Stratix 10 から追加された新しいレジスタです。

1入力1出力のシンプルなレジスタで、基本的な機能は ALM レジスタと変わりません。

Stratix 10 内には、この Hyper-Register が多数配置されています。(その数は ALM レジスタの十倍以上!)

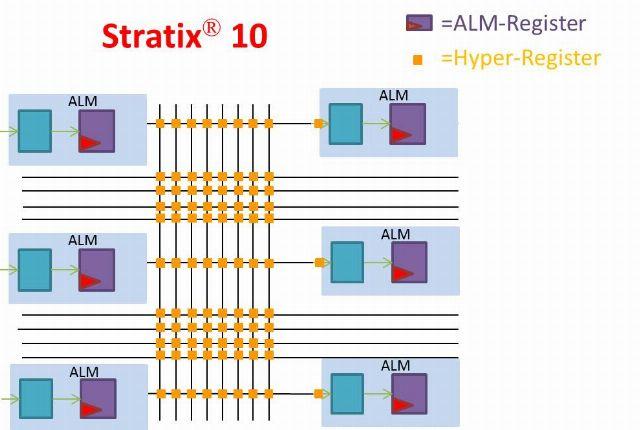

そして注目すべきは Hyper-Register の配置位置。

ここが上記の新機能を果たせるようになったポイントなのです。

Hyper-Register の配置箇所

さて、Hyper-Register はどこにあるのでしょうか?

このレジスタは ALM 同士を繋げる配線上に配置されております。

正確に言うと

・配線マトリックス (Row/Column) 交点

・すべてのブロックの入力

に配置されています。

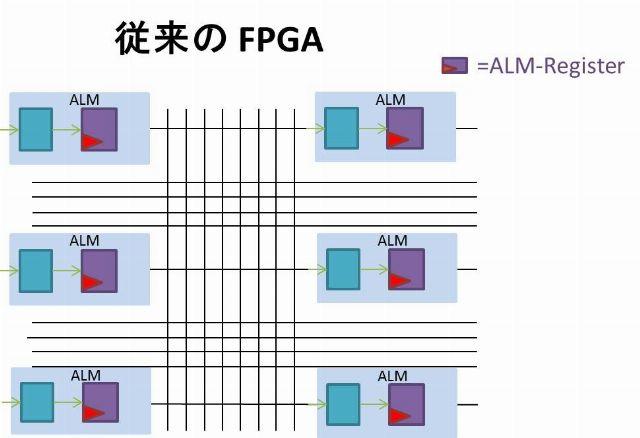

では、従来の FPGA の内部と比較して見てみましょう。

このようにして内部に配置されております。

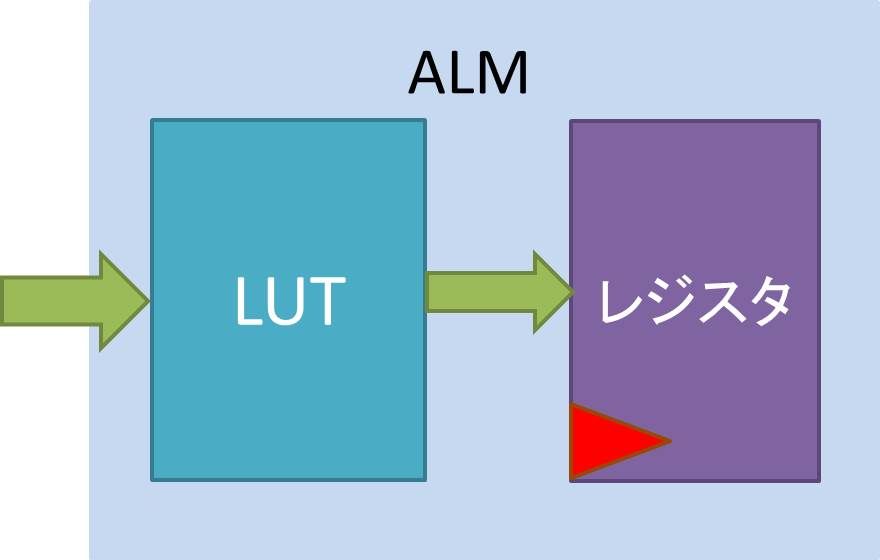

ALM とは?

補足として、ALM について少し説明します。

ALM は FPGA のロジック最小単位の一つで あり、以下で構成されています。

・LUT (ルックアップテーブル)

・加算器

・レジスタ

FPGA は ALM を組み合わせて、ユーザが記述した回路を実装しています。

Stratix 10 は ALM 内のレジスタと Hyper-Register 両方を持っています。

まとめ

Stratix 10 では Hyper-Register が柔軟に働き

・Hyper-Retiming

・Hyper-Pipelining

・Hyper-Optimization

などの新機能を実現し、パフォーマンス向上をさせることができます!

・HyperFlex

Stratix 10 から導入された FPGA のパフォーマンスを上げる仕組み全体のこと

・Hyper-Retiming、Hyper-Pipelining、Hyper-Optimization など

実際にパフォーマンスを上げるために働く機能

・Hyper- Register

上記の機能を実現するために Stratix 10 から導入されたレジスタ

今回は Hyper –xxが多く、記事作成中に混乱することが多々ありました…。

しかし皆様に理解していただけるよう、分かりやすい記事を目指して頑張ります!

次回記事では新機能の一つ Hyper-Retiming について紹介予定です!

そこで Hyper- Register が具体的にどのように働いているのかが明らかに!?

要チェックですよ!