こんにちは。

マクニカでインテル® FPGA 製品の技術サポートをしている インテル・F・ハナコ です。

みなさんは、インテル FPGA のピン配置において、いくつかのガイドラインがあることを知っていますか?

例えば、その一部をご紹介すると、

一、 同一の I/O バンク※ には同じ電位の I/O 規格をアサインすべし!

一、 差動(LVDS など)とシングルエンドの I/O 規格を同一 I/O バンクに共存させる場合は、ある一定の間隔(パッド※)を空けるべし!

など、デバイス・ファミリによりピン・レイアウトにルールがあります。

[参考情報] I/O バンクとは? / パッド (Pad) とは?

これらピン・レイアウトのガイドライン情報は Quartus® Prime に組み込まれているため、

コンパイルを実行することでピン・アサインの適合性が確認できます。

ですが、

フルコンパイルせずに、もっと効率よく確認する方法があります。

それが、Quartus Prime のピン・チェック機能 です。

ピン・チェック機能

Quartus Prime には、2つのピン・チェック機能があります。

いずれもフルコンパイルをすることなくピンの適合性を確認することが可能です。

| 概要 |

ユーザーのピン制約が基本的な I/O バッファ・ルールに違反していないかをリアルタイムに簡易チェックします。 Pin Planner に付加された機能で、ユーザーが Pin Planner 上でピン制約を入力すると即チェックが行われ、ワーニングやエラー・メッセージを報告するため、すばやく修正ができます。 Live I/O Check でエラーを修正後は、I/O Assignment Analysis でピン・アサインに対する最終的なI/O 適合解析を実施することを推奨します。 |

ユーザーのピン制約が I/O ルールのフルセットに対して適正かを本格的に “解析” します。 Live I/O Check 機能よりも検証項目が多く、デザイン・ファイルが使用可能な場合は、この検証により、デザインの I/O ピンと周辺ロジックについてより徹底した正当性チェックを実行することができます。 |

|

Quartus Prime Standard / Lite Edition |

〇 (Stratix® IV、Arria® II、Cyclone® 10 LP、 Cyclone IV、MAX® 10、MAX V、MAX II のみサポート) |

〇 |

|

Quartus Prime Pro Edition |

× |

〇 |

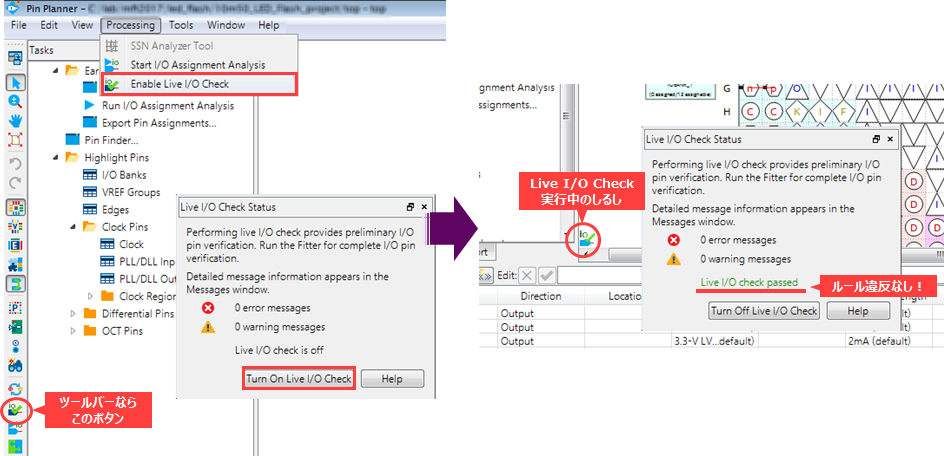

Live I/O Check

※ 事前に Analysis & Synthesis(Processing メニュー > Start > Start Analysis & Synthesis)以上のプロセスが実行されている必要があります。

Live I/O Check 機能の操作は、以下のとおりです。

① Pin Planner を起動します。(Assignments メニュー > Pin Planner)

② View メニュー > Live I/O Check Status Window を選択し、ウィンドウを表示させます。

③ Live I/O Check Status ウィンドウ内の Turn On Live I/O Check ボタン、

または Pin Planner 上の Processing メニュー > Enable Live I/O Check ボタンをクリックし、ピン・アサインのチェックを実行します。

④ デザインで使用するユーザー I/O ピンや未使用ユーザー I/O ピンのアサイン (ピン番号、I/O 規格、Reserved オプションなど) を行います。

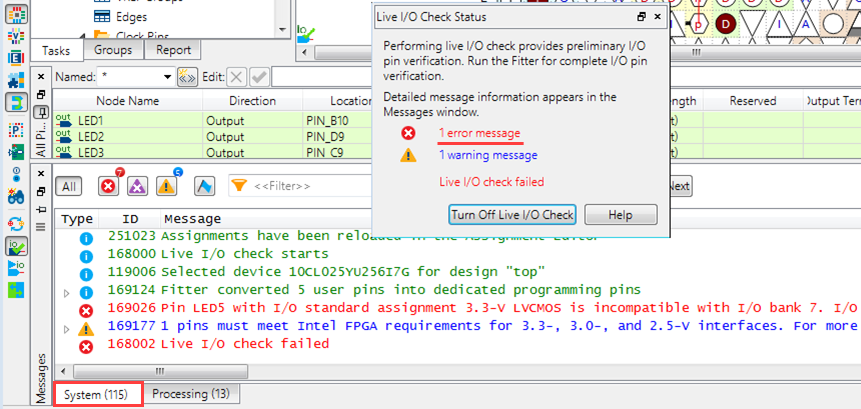

その都度チェックが行われ、I/O ルールに違反している場合は、Live I/O Check ウィンドウにエラーまたはワーニング・メッセージの数が

表示されます。同時に Pin Planner 上に現れた Messages ウィンドウ (System タブ) に、その内容がアナウンスされます。

メッセージの内容を確認し、メッセージのヘルプを活用しながら問題を回避します。

⑤ Live I/O Check ですべてのエラーを回避したら、I/O Assignment Analysis を実行し、さらに I/O ルールの検証を行います。

(I/O Assignment Analysis による検証後は、コンパイルを必ず実行してください。)

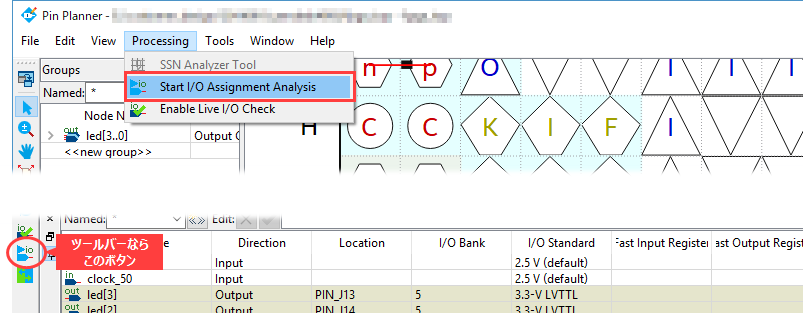

I/O Assignment Analysis

※ 事前に Analysis & Synthesis(Processing メニュー > Start > Start Analysis & Synthesis)以上のプロセスが実行されている必要があります。

また、ピン・アサインやピンに対するオプション設定などの制約を完了しておいてください。ターゲット・デバイスが Live I/O Check 機能を

サポートしている場合は、先に Live I/O Check を実行し、ピンに関する適合性の簡易チェックを行うことを推奨します。

I/O Assignment Analysis 機能の操作は、以下のとおりです。

① Pin Planner を起動します。(Assignments メニュー > Pin Planner)

② Processing メニュー > Start > Start I/O Assignment Analysis を実行します。

③ 解析が実行されます。

エラーやクリティカル・ワーニングがなければ、ピン制約は I/O ルールに適合しています。

コンパイル・レポートには Fitter レポートが生成され、ピン・フィッティング結果が確認できます。

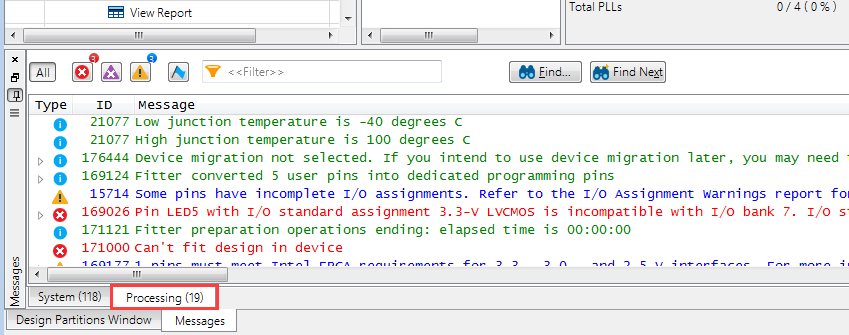

もしエラーやワーニング・メッセージが発生した場合は、Quartus Prime の Messages ウィンドウ (Processing タブ) に表示されます。

メッセージの内容を確認し、メッセージのヘルプを活用しながら問題を回避します。

I/O バンクとは?

インテル FPGA は、入出力ピン (ユーザー I/O ピン) 専用の電源が 1つのデバイスに対して複数本あります。

ユーザー I/O ピンの電圧は、FPGA が周辺 IC の様々なインターフェースに対応できるように考慮され、色々な電圧を選択できるようになっています。

例えば、Quartus Prime において あるユーザー I/O ピンを LVTTL で使用する制約を行い、ボード上に実装したデバイスの I/O 電源に 3.3 V を供給することで、LVTTL に準拠した I/O ピンを実現できます。

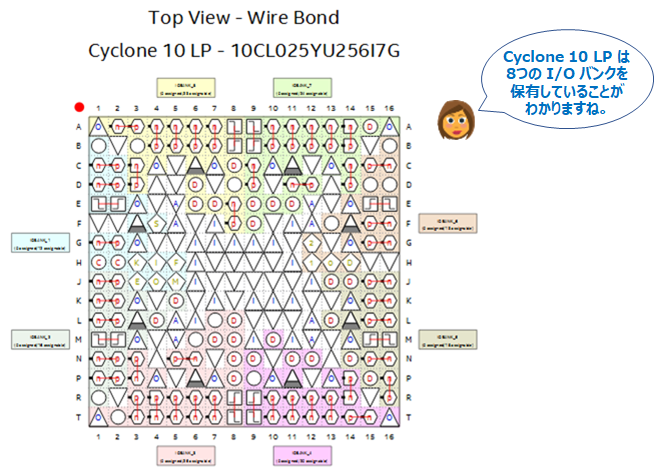

デバイスが保有するすべてのユーザー I/O ピンはいくつかのグループに分割され※、この I/O グループを “I/O バンク” と言います。

各 I/O バンクはそれぞれにユーザー I/O 用の電源を持ち※、個別に異なった電源電圧を供給できるため、1つのデバイスに対して複数の I/O 規格をサポートできます。(※ MAX 7000 ファミリ、MAX 3000A ファミリ、FLEX シリーズ、ACEX ファミリのユーザー I/O ピンは、グループに分割されていなく、I/O 用電源すべてに同じ電圧を供給しなければなりません。)

各 I/O バンクは番号やアルファベットで識別されていて、その I/O 用電源にも同じ番号やアルファベットが使用されているので、どの電源がどの I/O バンクの供給電源なのかが明確になっています。

なお、1つの I/O バンクに属するすべてのピンは、同じ電位の I/O 規格でなければなりません。

どのユーザー I/O ピンが どの I/O バンクに属するのかは、メーカーのホームページで公開されているドキュメント Device Pin-Out Files で確認できます。

また、Quartus Prime において、Pin Planner の Package View は I/O バンクが色分けされているので、ユーザーがピン・レイアウトしやすい仕様になっています。

パッド (Pad) とは?

インテル FPGA デバイスのパッケージ・ピンは、シリコン・ダイの最上部メタル層に接続されていて、その接続部分を “パッド” と言います。

各パッドはパッド ID によって識別され、パッド ID の番号は 0 から始まり反時計回りに 1 ずつ増えます。

シグナル・インテグリティの問題を防止するために、Quartus Prime はピン配置ルールを使用して、ピン配置とピン関連アサインメントの妥当性を検証します。(参考: Live I/O Check、I/O Assignment Analysis)

ピン配置ルールには、パッド・ロケーション (パッド間隔) に制限がなされているものもあるので、ユーザーは、ピンがどのパッド・ロケーションに割り当てられているか把握することが重要です。

例えば、特定のデバイスでは、シグナル・インテグリティを確保するために、VREF パッドがサポートする I/O ピン数が制限されています。また、シングルエンド入力ピンまたは出力ピンと、差動ピンとの間のパッド数にも制限があります。

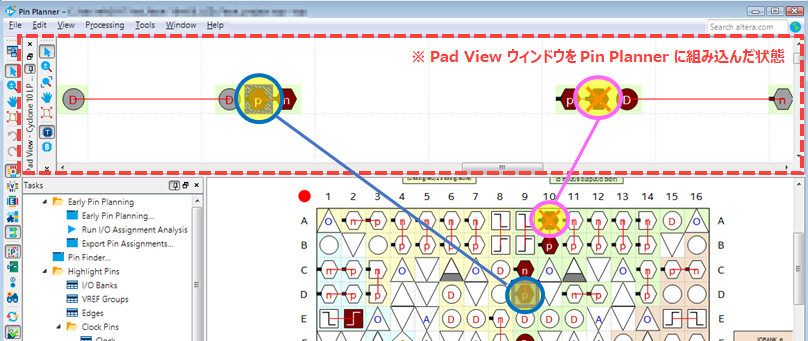

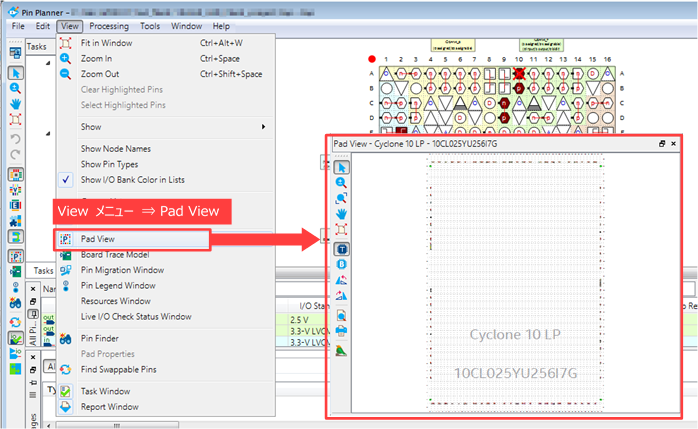

Pad View ウィンドウ

パッケージのピン・レイアウトで隣接したピン番号であっても、パッド・レイアウトは隣接しているわけではないため、パッドと言う観点でレイアウトを検討する際には、パッド・ロケーション専用ビューワ “Pad View” の活用をオススメします。

Quartus Prime の Pin Planner 上から、View メニュー > Pad View により表示します。(パッケージ・ビュー上で右クリック > Pad View でも OK!)

ピン配置ルールに沿ってピン番号を決めるときや、I/O Assignment Analysis 機能などによりパッド・ロケーションのエラーが発生したときなどに使用してください。

パッケージ・ビューと Pad View は連動して表示されます。