こんにちは!とぷぅです。

前回は IP の使い方について簡単にご説明いたしました。

IP の基本的な生成方法、使い方を知ってからはデザイン記述への抵抗が少なくなりました。

また IP に関するサポートも担当することが出来るようになり、うれしく思っています。

先日、ステートマシンを使って、シーケンスを組んでいくサポートを行うことになりました。

ステートマシンは研修で習って以来使用してなかったので、書き方のイメージしか浮かばず、

細かい文法などは思い出せませんでした。

「研修のときの資料を見返すか…」

と思い、資料を探していたところを先輩に目撃されました。

先輩 「何を探しているの?」

とぷぅ 「研修時の資料です。ステートマシンの書き方を忘れてしまって……」

先輩 「資料探すよりも早く書き方が分かって、簡単に記述をする方法があるよ」

と、方法を教えてくれました。

それはDesign Template という便利な機能です。

今回はその使い方についてご説明いたします。とても簡単です。

1.Design Template の使い方

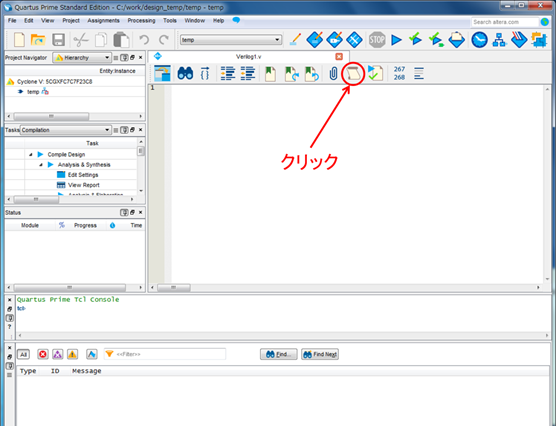

1 - 1. Text editor を開き、Editor の上部の Insert template のマークをクリック。( 図 1 )

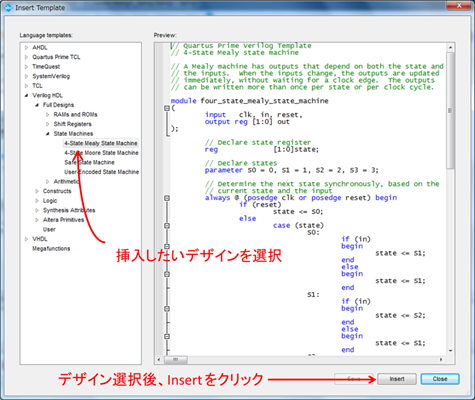

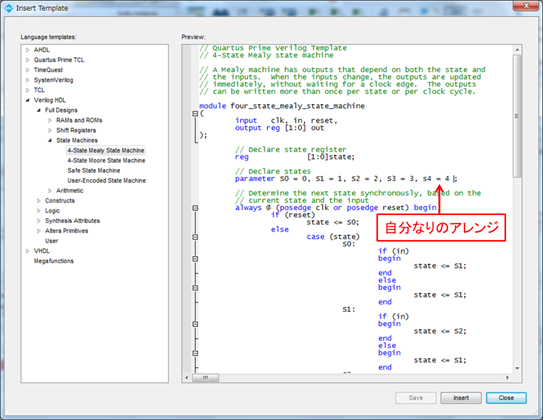

1 - 2. 図 2 のような画面が出てくるので、自分が挿入したいテンプレートを選択。

今回は例としてステートマシンのテンプレートを挿入します。

Verilog → Full Designs → State Machines → 4 - State Mealy State Machine を選択し(プレビュー画面の中に HDL が表示されます)、Insert をクリック。

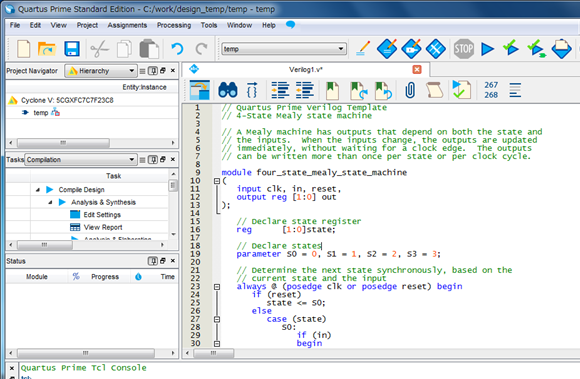

1 - 3. テキストエディタに選択したデザインが挿入されます。( 図 3 )

あとは、モジュール名や信号名などを自分の回路仕様に合わせて編集し、ステートマシン動作を記述していくだけ!

非常に簡単です。

他に挿入できるテンプレートとしましては VHDL や System Verilog などのハードウェア言語はもちろん、tcl コマンドや SDC 制約のコマンドもありました。

私はこの便利さに感動しつつ、いろいろな項目を見ていくうちにあることに気づきました。

それは各項目の中に User というものがあるということです。

これはその名の通り、ユーザがテンプレートを作成し、保存できる機能です。

今回はその使い方をご説明いたします。(私は User の項目を選択し、Preview にコードを入力すれば良いと思っていましたが、そうではありませんでした......)

2.ユーザ・テンプレートの作り方

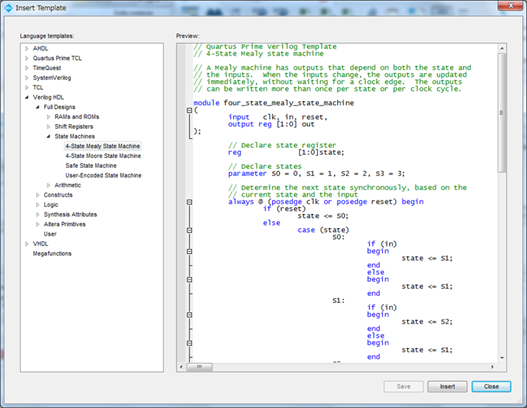

2 - 1. まずはベースとなるテンプレートを選択します。今回は先ほどの例でも選択した 4 - State Mealy State Machine を再度選択します。( 図 4 )

2 - 2. Preview ウィンドウ内で編集し、close を選択します。今回は例として s4 = 4 という記述を加えました。( 図 5 )

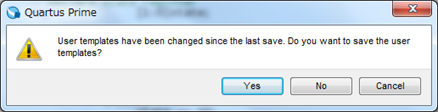

2 - 3. Close をクリックした後、ユーザ・テンプレートとして保存するかどうかのメッセージが表示されるので Yes をクリック ( 図 6 )。

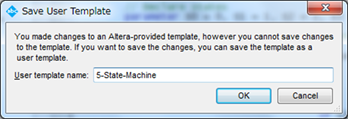

その後 User template name にテンプレートの名前を入力します( 図 7 )。

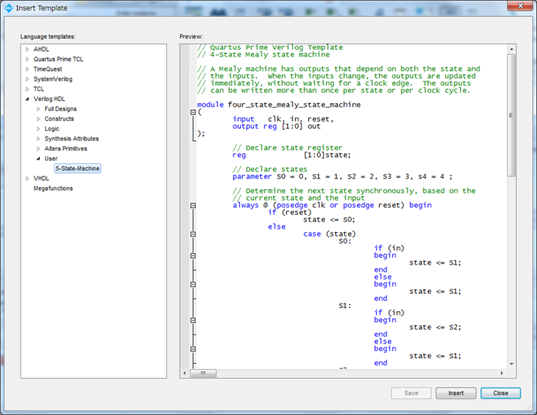

2 - 4. User の項目にテンプレートが追加されます。( 図 8 )

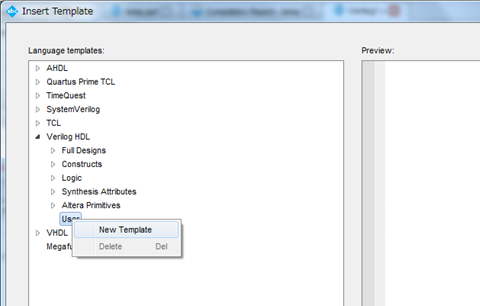

このように既存テンプレートを編集し、ユーザ・テンプレートとして保存する方法以外にも User の項目を右クリックし、New から新規作成する方法もあります (図 9 )。

2 - 5. ユーザ・テンプレートの保存ディレクトリを指定する。

ユーザ・テンプレートの保存場所は Tools → Options → Text Editor の User templates library directory で保存先のディレクトリを指定することにより変更可能です。(デフォルトはプロジェクトディレクトリ内です。)

別のプロジェクトでユーザ・テンプレートを使用することもできます。

その場合は新規プロジェクト作成時点でユーザ・テンプレートが保存されているディレクトリを指定してくれています。

エディタ画面の上部にこんな便利な機能が隠れているとは思いませんでした。

まとめ

・ design template を用いれば、設計工数を削減できる

・テンプレートは RTL 記述だけでなく、SDC 制約コマンドや Tcl コマンドもあるので

ちょっとコマンドを忘れてしまったときなどに便利

・自分のオリジナルのテンプレートを作成し、使いまわすことが可能

とぷぅの他の記事

|

『IPをつかってみよう~IPの中身を見たい~』 | |

|

IP の中身を見るために奮闘したお話。

|

||

|

『テストベンチアレルギー解消』 | |

|

テストベンチのコツをつかめる記事です。 |

||

|

『タイミング解析~ FPGA の入力遅延の定義~』 | |

|

タイミング解析の入出力遅延についてまとめました。 |