はじめに

こんにちは、マス男です。

今回の赤面エピソードは初めて FPGA の内蔵メモリ・ブロックについて勉強したときに思ったことをお話しします。

FPGA デバイス内部にはメモリ・ブロック(=メモリとして使用する専用領域)が組み込まれています。

図1. Cyclone® IV 内部構造

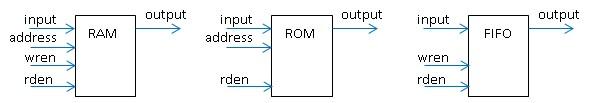

ユーザは、このメモリ・ブロックで以下の3種類のメモリを実現することが出来ます。

・RAM ( Random Access Memory ) : 指定したアドレスに対してデータを書き込み・読み出すことが出来るメモリ.。電源を OFF にするとデータが消去する揮発性である。

・ROM ( Read Only Memory ) : 指定したアドレスのデータを読み出すメモリ。電源 OFF にしてもデータが残る不揮発性である。あらかじめ ROM 内部にデータを書き込む必要がある。

・FIFO ( First-In First-Out ) : 書き込んだデータの古い順から読み出すメモリ. アドレスの概念がない。

メモリ・ブロックは Quartus® II の Tools メニュー ⇒ MegaWizard Plug-In Manager からデザインすることが出来ます。

FPGA のメモリ・ブロックは 3種類のメモリ ( ROM、RAM、FIFO ) を実現するなんて不思議に思いました。

ここでマス男はひらめきました。

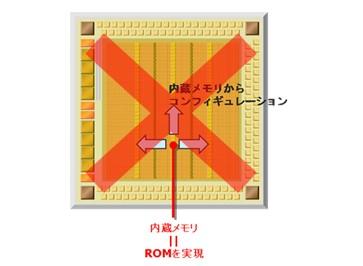

「 ROM は電源 OFF にしてもデータは消えない。だったら、 FPGA のメモリ・ブロックで ROM を実現し、回路データを書き込む。メモリ・ブロックをコンフィグレーション用メモリとして使用することが出来るのではないか?」

図2. マス男の赤面イメージ

先輩社員にマス男の考えを話しました。

先輩社員 「 FPGA は SRAM 構造であり、電源 OFF にしたらデータが消える揮発性です。同様に内蔵メモリ・ブロックも SRAM 構造です。メモリ・ブロックの物理構造が ROM 構造に変化するわけではないからね(笑)。」

つまり、内蔵メモリ・ブロックは SRAM 構造であり、 Write Enable 信号や Address 信号の接続の有無を自在にプログラムすることで ROM や FIFO のように動作(振る舞い)していたのであった!

・書き込み信号 ( Write Enable ) が無い SRAM が、ROM のように動作している

・アドレス信号 ( Address ) が無い SRAM が、FIFO のように動作している

マス男 「メモリ・ブロックの物理構造が変化すると勘違いしました(恥)。メモリの制御信号の接続の有無を自在にプログラム出来るのが FPGA の醍醐味ですね!コンフィグレーション用デバイスは不揮発性の ROM だから、 SRAM のメモリ・ブロックでは駄目なのですよね。」

先輩社員 「 ROM でコンフィギュレーションできるというのは正しくないな。 ROM といっても、様々な物理構造があるのは分かっている?メモリの種類について調べてごらん。」

図3. メモリの種類

マス男 「コンフィギュレーション用デバイスはフラッシュ ROM 構造なんですね!」

学んだこと

・アルテラ社製 FPGA の内蔵メモリ・ブロックは RAM、ROM、FIFO を実現できる

・内蔵メモリ・ブロックは SRAM 構造であり、 Write Enable 信号や Address 信号の接続の有無を自在にプログラム

することで ROM や FIFO のように動作できる