アルティマの新人エンジニアの一人、頭領は仕事を終え、電車の中で居眠りをしていた…

意識が飛ぶ中、製作実習の事に思いをはせていると一点確認したい事がでてきた。

「 FPGA の I/O Standard は 3.3 V LVTTL になっているのか」

この間、新人 3 人で話していた時に出てきた話題だ。あの時はたしか… Fitter Report で確認が必要という結論に達したのだった…

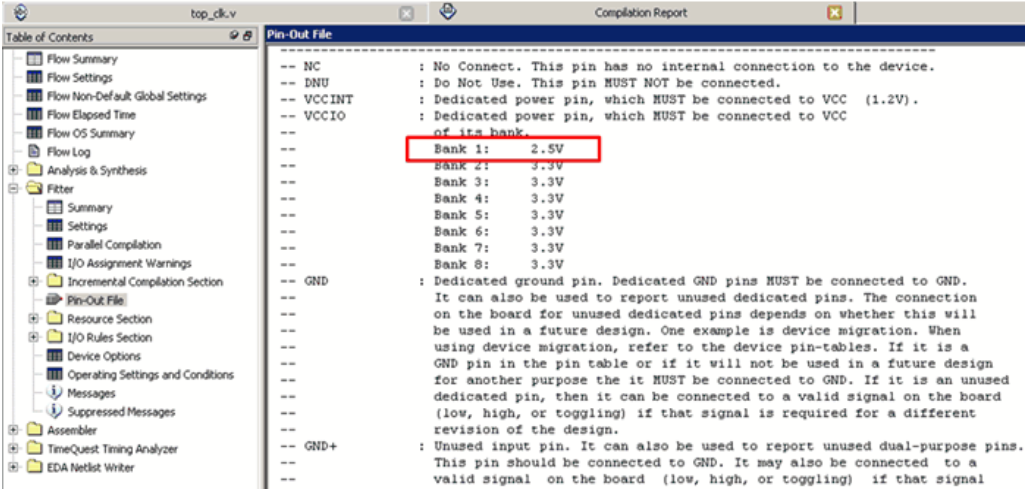

翌日、製作実習で作成したデザインのうち、いくつかのピン配置、 I/O Standard を Fitter Report → Pin-Out File で確認してみた。すると…

あれっ!このデザイン、 I/O Bank 1 だけ I/O Voltage が 2.5 V になってる!

「 2.5 V になるような設定をしてないのに…」 何故だろう・・・

!? もしや逆? 2.5 V 以外の電圧に設定してないだけじゃないのか! 「設定してない」…

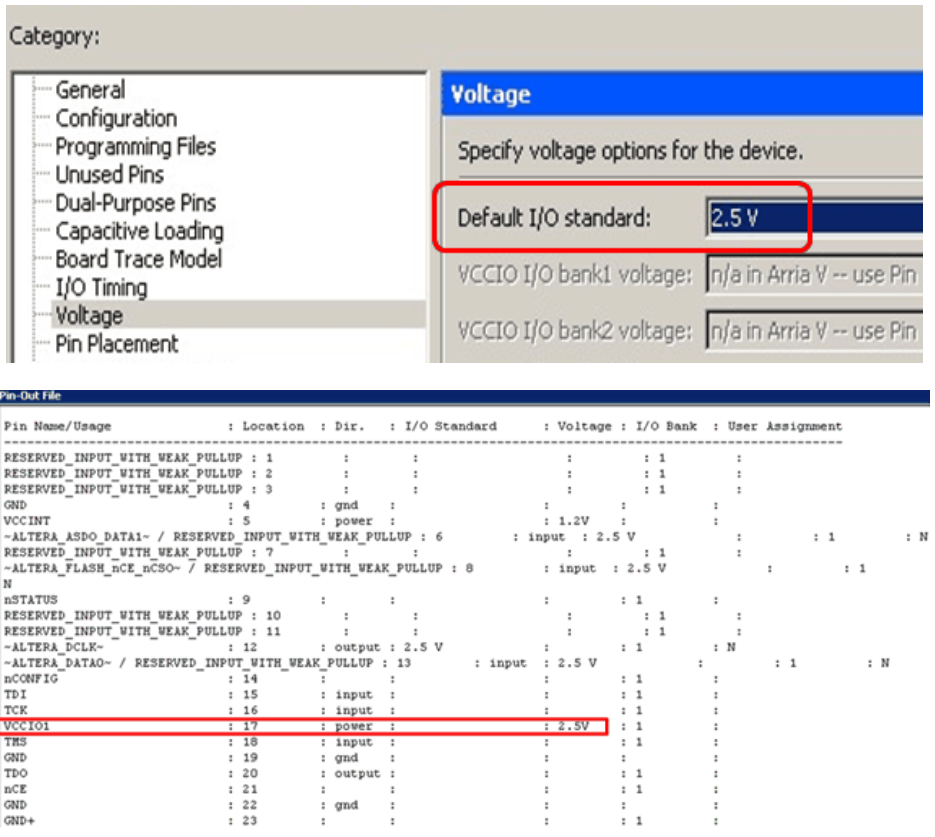

あ、こないだ教えてもらった、「 Device and Pin Options 」で I/O Standard のデフォルト設定を変更していないからこうなったのか!

1 つの I/O バンクで設定できる VCCIO の電圧レベルは 1種類だけ。つまり、使用する User I/O の I/O 規格が決まった時点で、そのバンク内の VCCIO は決まってしまうのだ。例えば、 SSTL-18 と 1.8 V の設定を行ったピンが属する Bank の VCCIO = 1.8 V となる。

今回、 Bank 2 ~ 8 では User I/O を使用し、 I/O Standard を Pin Planner にて 3.3 V LVTTL と設定したため、Quartus® II はこれらのバンク内の VCCIO が 3.3 V だと自動的に認識した。

しかし、 Bank 1 では User I/O を使用していないため、User I/O の I/O Standard から VCCIO の電圧レベルが決まらない。

この場合、Quartus® II はデフォルト設定の値を VCCIO に適用する。通常、設定を変更していない場合、デフォルトの設定は 「 2.5 V 」 になっている。

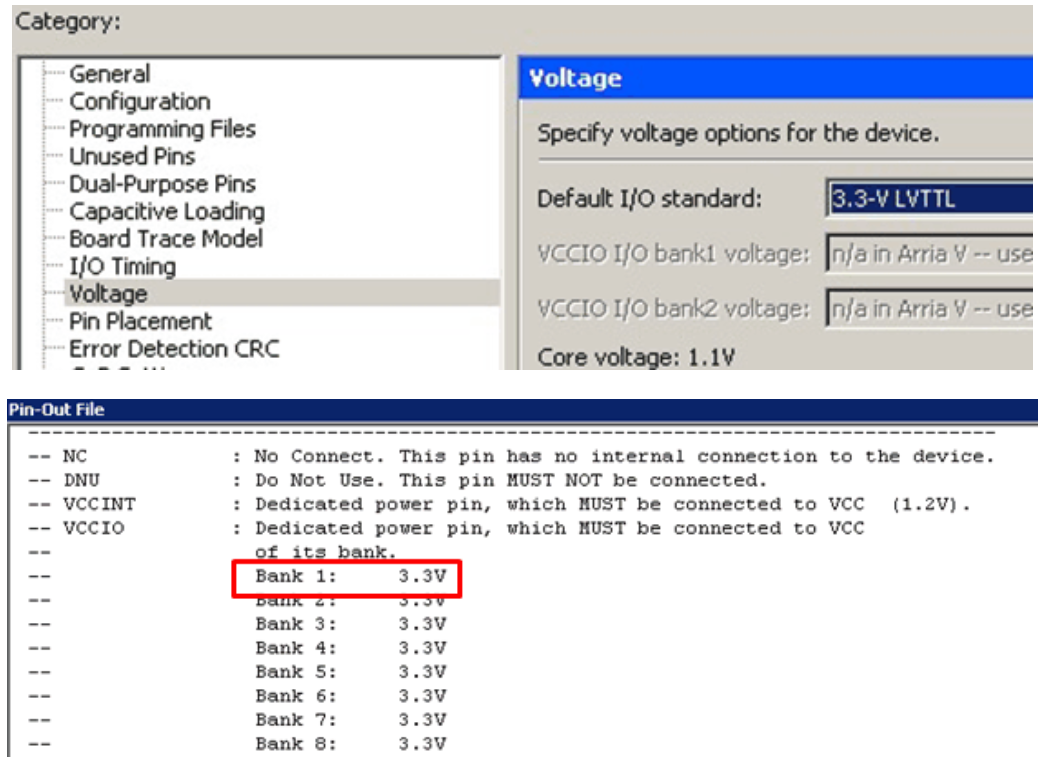

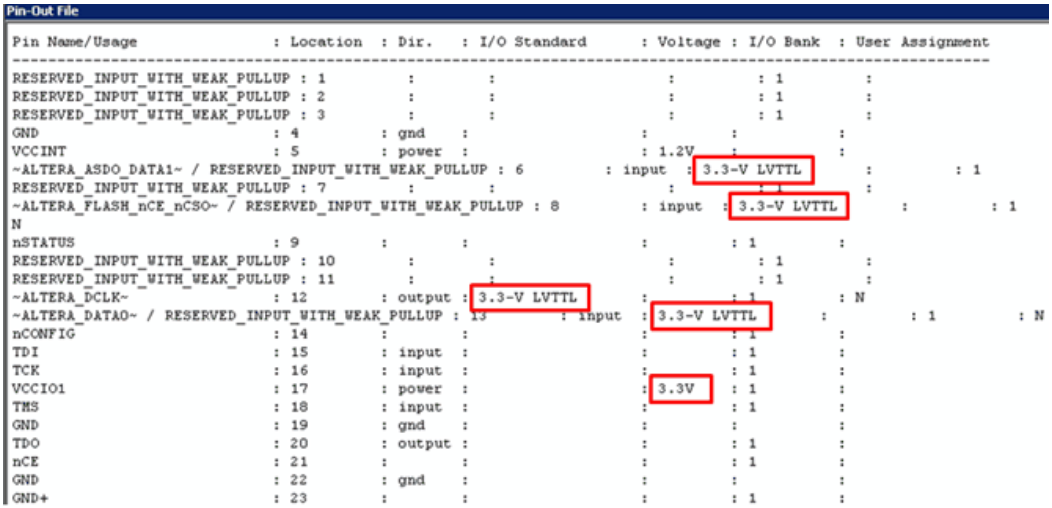

その為、デフォルト設定の値を 「 Device and Pin Options 」 Voltage → Default I/O Standard で 3.3 V LVTTL に変更したところ、Fitter Report にもその変更が反映された。

デフォルトの I/O Standard 設定によって 2.5 V のままだった、Bank 1 の規格とその電圧もこの通り。期待通りの 3.3 V LVTTL に変更された。

コンパイル前に Assignment Editor や Pin Planner 等で詳細の設定を行っても、デバイス全体のオプション設定が反映される箇所がある。

その為、設定が仕様通りになっているか確認を行うために、Fitter Report があるのだ!

こうして、新人エンジニアの頭領は、コンパイル後には必ず 「 Fitter Report 」 の 「 Pin-Out 」 で規格等をチェックする習慣がついたのだった。