こんにちは。

アルティマに入社し、様々な場面で様々な名前の規格を耳にしてきました。

アルテラ社 FPGA を使用するにあたって重要な 「 I/O Standard 」 について、頭でっかちの頭領が、妙な部分に疑問を持ちつつも理解を深めていったエピソードを紹介します。

技術研修を行っていた頃、 Quartus® II を使用する際にちょくちょく出てきた 「 I/O Standard 」。

規格によって電気的特性が異なるようだが、まだイメージがふわっとしていて、疑問がたくさん浮かんでくる。

まず、エレクトロニクスの世界に飛び込んだばかりの頭領は、 I/O Standard を使いこなす以前に、これらの使用目的に疑問を感じていた。

疑問1. そもそも、それぞれの I/O Standard が、どんな用途に使われているのだろう?

そもそも、I/O Standard が何の目的で存在しているのか、研修中はさっぱりわからなかった。

しかし調べてみると、アルテラ社 FPGA でサポートしている I/O Standard の使用例に関しては、デバイスのハンドブックにしっかり記載されていた…

そこで、各 I/O Standard の大まかな用途を抜粋してみた。

今まで何も考えずに I/O Standard を選んできたけど、用途が全く異なってくるんだなあ。

疑問2. 各種入力信号の High / Low は FPFA によってどう認識され、その基準値はどこに定義されているのか?

信号の種類は大きく分けると、シングルエンド、差動電圧 2種類がある。

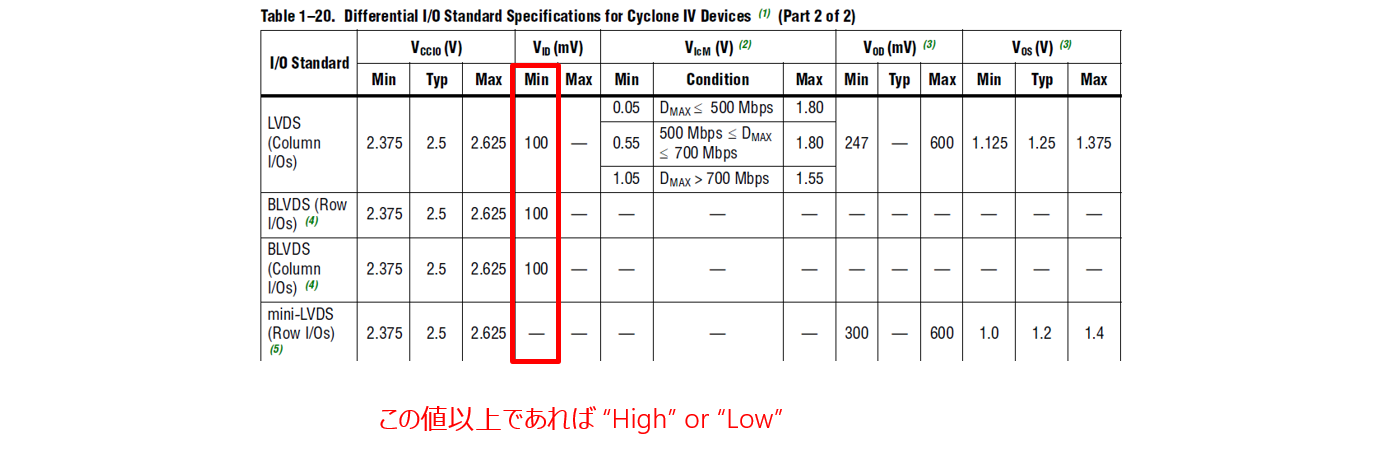

アルテラ社の FPGA では、Device Datasheet をダウンロードし、 Operating Conditions の I/O Standard Specifications を参照することで、各規格の電気的な仕様が確認できる。(アルテラ HP の画面右上 「資料(英語版では “ Documentation ” )」 をクリックし参照)

・シングルエンド: LVTTL 、 LVCMOS 、 PCI-X など

1つの信号が、規格に定められた一定の電圧値より高ければ High 、低ければ Low として FPGA に認識される。入力信号の High / Low は、 VIH と VIL を基準としている。

・差動電圧: LVDS 、 BLVDS 、 mini-LVDS など

2つの信号の電位差が一定の値以上であれば、High あるいは Low と認識される。Datasheet の VID を参照する。

あれ… mini-LVDS に VID の記載がないのはなぜだろう…

疑問に思い、 Datasheet を下にスクロールしてると…

あ、 Cyclone® IV においては、 mini-LVDS は出力ピンしかサポートしてないのか!

I/O Standard にもいろいろあるけど、デバイス・シリーズや I/O Standard によっては、一部サポートが制限されるのもあるから、データシートをよくチェックしないと!

ところで、 Datasheet を読んでいると「リファレンス電圧」を使用する I/O Standard が存在するみたいだけど、調べてみるとどうやらこれはリファレンス電圧ピンに基準電圧を入力し、それを基準として High / Low を定義するもののようだ。

上記データシートの VREF 値を参考にし、電圧を入力する。VREF って、どこかで見たような…

そうだ!製作実習をしていた頃、デバイス・シリーズの Pin Connection Guidelines を参照した時に電源供給のピンとしてよく見かけたやつだ!

リファレンス電圧形式の I/O Standard を選択した時は、このガイドラインを参照して、記載されているピンにデータシートに記載されている通りに電源を供給しないといけないのか!!だんだん繋がってきたぞ!!

…とぶつぶつ呟いていたら、先輩がもう一つ質問を投げかけてきた。

先輩 「じゃあ、Quartus® II 上で I/O Standard を 2.5 V に設定し、基板上では VCCIO に 3.3 V を供給したら、実機上ではどうなるでしょうか??」

頭領 「うぐっ… (じ、実機上…?ピン情報は Quartus II 上で詳細に設定できるから、それに従えばいいはずだけど、逆に Quartus II の指示に従わなかった場合、どうなるんだろう…?)」

と、頭領は錯乱状態に陥っていたが、その答えはアルティマが作成した資料にあっさりと記載されていたのだった。

そうか、Quartus II 上での設定は実機上のデバイスの電圧を決めているわけではないのか!

つまり、もし Quartus II にて I/O Standard を 2.5 V に設定したとしても、実機上で VCCIO に 3.3 V を供給したら、該当する I/O バンクの電圧は「 3.3 V 」になるのだ!

でも、1つの I/O バンク内では 1種類の VCCIO しか使用できないし、 FPGA デバイスの仕様を守るために、アルテラ FPGA の各デバイスの特性が搭載されている Quartus II 上でピンの設定を行い、コンパイルレポート内「 Fitter Report 」の「 Pin-Out File 」をチェックしたほうが良さそうだなぁ。

このように、こんな「頭でっかち」の新入り技術者でも、「デバイスに対して従順な」 Quartus II があるおかげで、「ツールに対して従順に」設計を行っていけば良いのである。