こんにちは、ハチです。

前回は Power On Reset (POR) について勉強しました。

イニシャライズの時間はどのようにして決まっているのでしょうか。

ハンドブック内でイニシャライズを検索すると、以下のページがヒットしました。

Configuration -> Cofiguration Process -> Initialization

(「Configuration and Remote SystemUpgrades in Cyclone IV Devices」より)

After the configuration data is accepted and CONF_DONE goes high, Cyclone IV devices require 3,192 clock cycles to initialize properly and enter user mode.

ハンドブックに書いてあるとおり、イニシャライズにかかる時間はクロック 3192 サイクルです。

では、クロックの周波数が分かればイニシャライズ時間が計算できそうです。

そこで以下のような仮説を立ててみました。

"AS モードのコンフィギュレーションでは FPGA からクロック (DCLK) を供給しているので

イニシャライズ時のクロックも FPGA 側から供給されているのではないか?"

私の仮説は半分正解だったようです。

イニシャライズのクロックは内部クロック (DCLK) と外部クロックの二種類が選べます。

それぞれの場合についてみていきます。

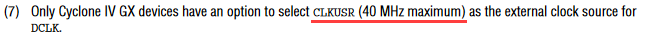

※ AS モードでは CLKUSR は Cyclone® IV GX シリーズのみサポートしています。

In Cyclone IV devices, the initialization clock source is either the internal oscillator or the optional CLKUSR pin. By default, the internal oscillator is the clock source for initialization.

内部クロック (DCLK を使用)

内部クロックを使用する場合は、MSEL ピンにて Fast / Standard のどちらのモードでコンフィギュレーションするかで周波数が変わってきます。

また、下記の DCLK については Altera のホームページに記載がありました。

・ Fast Mode の場合・・・ Max 40MHz, Min 30MHz

・ Standard Mode 場合・・・Max 20MHz, Min 10MHz

私の基板上では Standard Mode で設計してあるため、イニシャライズ時間は次のように計算できます。

イニシャライズ時間 = クロックの立ち上がり数 * 周波数

・ Worst Case : 3192サイクル * 100ns (10MHz) = 319.2us

・ Best Case : 3192サイクル * 50ns (20MHz) = 159.6us

さて、イニシャライズが終わるまでの時間が分かりました。

もう一度おさらいして、火を入れてからユーザモードになるまでの時間 (Worst Case) を見ていきます。

ユーザモードになるまでの時間 = POR Time + コンフィギュレーション時間 + イニシャライズ時間

= 200ms + 147.2ms + 319.2us

= 347.5ms

外部クロック

外部クロックの周波数が決まらないとイニシャライズ時間も求められません。

では、自由にクロックの周波数を選べるのでしょうか?

極端な話、1GHz 入れても大丈夫なの?さすがにそんなことはありません。

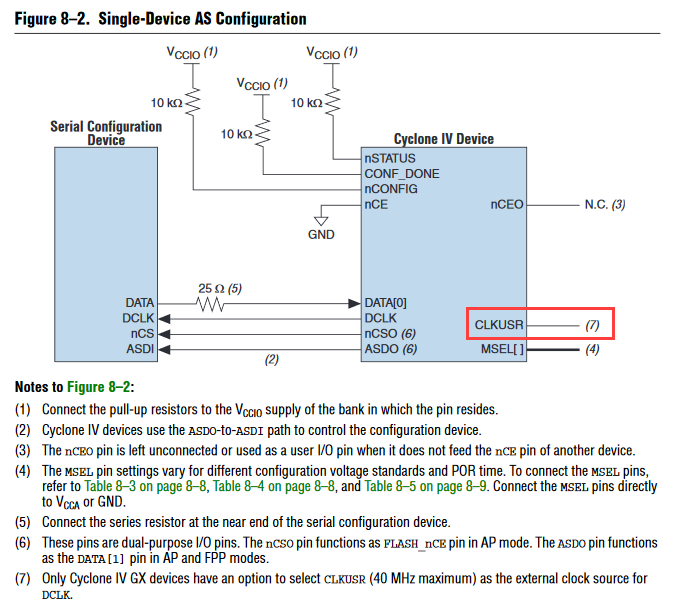

きちんとハンドブック内で規定されており、外部クロックも Max 40MHz です。

下記がその文章です。

Configuration -> AS Configuration -> Single Device AS Configuration

(「Configuration and Remote SystemUpgrades in Cyclone IV Devices」より)

では、外部クロックを使用する場合はどのように接続するのでしょうか?

ハンドブックと Pin Conection Guidline を調べてみました!

基本的には内部クロックを使用する場合と同じ接続です。

Pin Conection Guidline によるとこのピンを使用する場合は発振器と接続すればよいようです。

未使用の場合は GND に接続する必要があります。

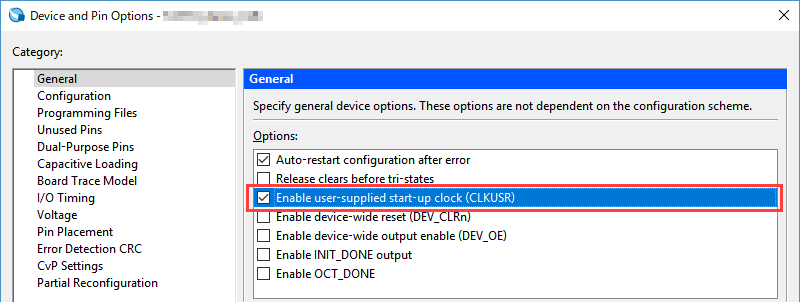

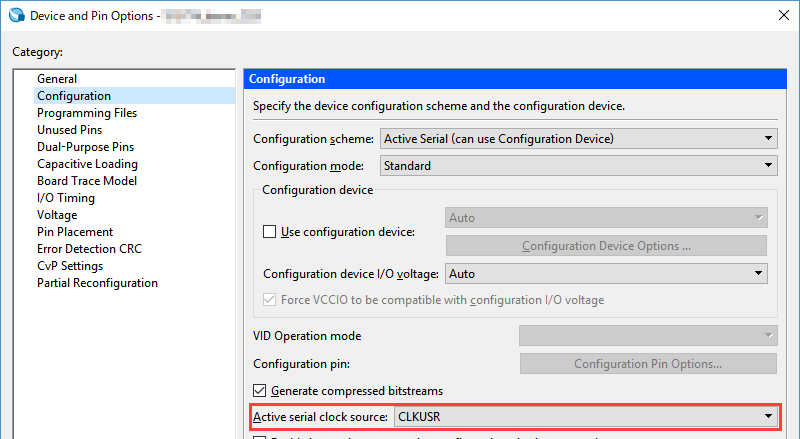

また、Quartus II でも設定が必要なようです。実際に Quartus II で設定を行ってみました。

以下の 2つの手順で CLKUSR ピンの使用・未使用を設定できます。

・ Asignment -> Device -> Device & Pin Options -> General にて CLKUSR のチェックを入れる

・ Asignment -> Device -> Device & Pin Options -> Configuration -> Active serial clock source にてクロックの選択

(※ このオプションは、Cyclone IV GX のみサポート)

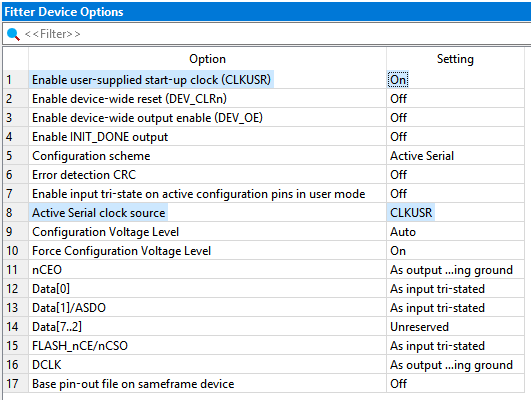

上記の設定を行ってコンパイルを実行すると、確かにレポートに情報が吐き出されました。

確認方法は次のとおりです。

Compilation -> Fitter -> I/O Rules Section -> Device Option

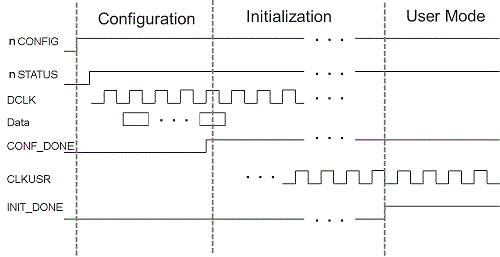

外部クロックはどのタイミングで入れて、どのタイミングで止めればいいのだろうか?

PS モードと FPP モードのコンフィギュレーションのタイミングチャートを見ると、 DCLK 4 サイクル経った後に CLKUSR がイネーブルになります。

さらに、イニシャライズが終わってから外部クロックを止めたい場合は INIT_DONE ピンを見て止めるのがよさそうです!

下記の図がコンフィギュレーション信号の動きです。

これで火を入れてからユーザーモードになるまでの時間が分かりました!

しかしここで、新たな疑問がわいてしまいました。

POR は FPGA をリセットする時間。

イニシャライズは FPGA のレジスタをゼロ(初期値)を代入する時間。

この二点の違いが分からない…

リセットと初期化がどうも同じに見えてしまいます。

次回はイニシャライズと POR の違いについて勉強します。