C 言語の経験があったので、Verilog HDL の記述スタイルは理解しやすかったです。

大規模な論理回路の処理をプログラムで記述することができるので、回路図で記述するよりも非常に簡単に設計できるのですね!

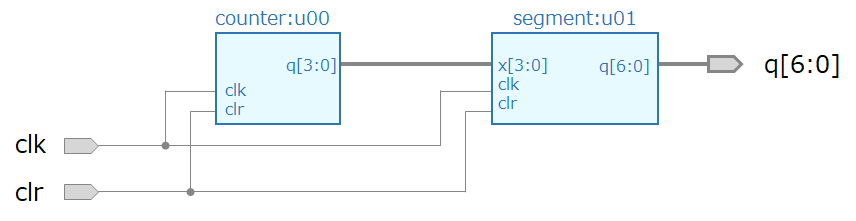

カウンター (counter:u00) とデコーダー (segment:u01) を使用した回路です。

counter と segment というモジュールを作成して、上位階層ファイルで呼び出し接続しています。

Quartus® II は論理チェック機能と論理合成を行うことができるため、Quartus® II を使って論理合成をおこなってみたところ、、、

4 bit の counter は論理合成。。。できました!

次の 7 bit のsegment は論理合成。。。が できません!

以下の Error が発生して、論理合成前の論理チェックで止まってしまいました。

Error (10137): Verilog HDL Procedural Assignment error at segment.v: object "out" on left-hand side of assignment must have a variable data type

どうやら segment モジュールの出力 out に原因があるようです。

もう少し詳しく知りたいなあ。。。

そんな時 先輩が一言。

先輩 「Help を見たら?」

ん? Help?そんな便利なものがあるのですか!?

やり方は、詳細を知りたい Error をハイライト後に「 F1 キー」を押すだけです!

F1 キーを押すことで (また右クリックから Help をクリックしても同様のことがおこなえます。)

Quartus® II の Help にあるエラー内容の解説を見ることができます。

すると今回は以下のような解説が出てきました。

|

ID:10137 Verilog HDL Procedural Assignment error at <location>: object "<name>" on left-hand side of assignment must have a variable data type CAUSE: In a procedural assignment at the specified location in a Verilog Design File (.v), you assigned a value to the specified object, which was declared with a net data type (wire, wand, and so on) rather than with a variable data type (reg, integer, and so on). In Verilog HDL, you must use continuous assignments when targeting nets, and procedural assignments when targeting variables.

ACTION: Declare the specified object with a variable data type, if that is appropriate, or use a continuous assignment to assign a value to the object. ~~~~~~~~~~~~ (要約) 原因: ネット型( wire, wand など)のものを変数型( reg, integer など)で宣言しています。 Verilog HDL では対象がネット型の場合は継続代入文で、変数型の場合は手続き代入文で使用しなければいけません。

対応策 : エラーの対象について変数型で定義するか、変数型で定義したものについて手続き代入文で記述してください。 |

ネット型を変数型に変更する?

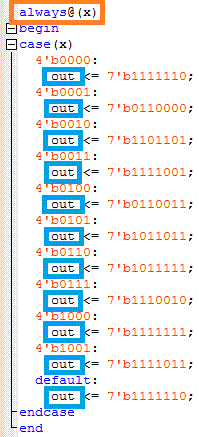

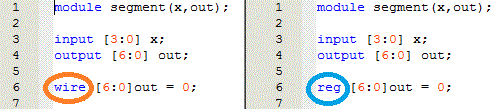

ここで segment モジュールを見直してみると、、、

always 文で出力 out を使っています!

出力 out は wire で宣言しているので、always 文では使うことができません。

always 文で使うために図3のように wire を reg に変更したら無事論理合成できました。

補足としまして、各文で使えるデータタイプ型は以下のとおりです。

継続代入文 (continuous assignment ) assign文: ネット型 ( wire, wand )

手続き代入文 (continuous assignment) always文: 変数型 ( reg , integer )

ちなみに過去の先輩も同じことで悩まれていました。

その後、上位階層を作成し、無事 RTL Viewer で図 1 の通りに回路を作ることができました。

Error は嫌ですけれど、原因が分かるとうれしいですよね。

みなさんも困ったときは「Error の上でハイライト(クリック)して F1 キー」押してみてください♪

新しい発見があるかも知れませんよ!

[ 今回のポイント! ]

Error をハイライト選択し F1 キー ⇒ Quartus® II の Help に飛んで詳細が確認できる。