こんにちは、マス男です。

“タイミング解析シリーズ” 最終回となりました。新人研修で最も難しかったのが、タイミング解析の講義でした。

本コラムでは、タイミング解析の講義資料やノートをまとめ、つまずいた点や有益な情報をご紹介したいと思います。

タイミング・エラーの原因は?

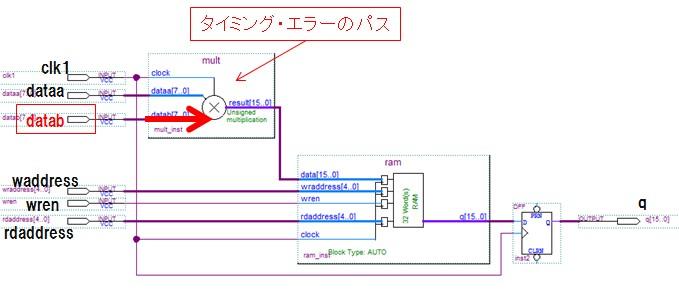

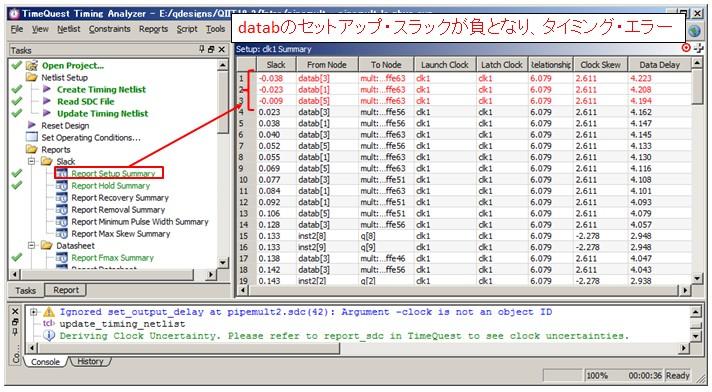

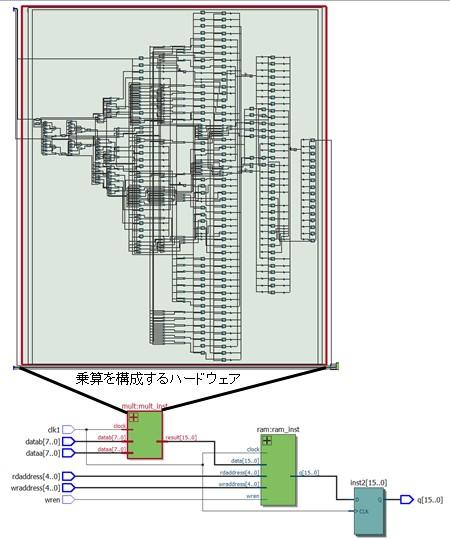

動作周波数 165.5MHz で動作する乗算器と RAM のモジュール( 図1 )をデザインし、タイミング解析したところ、datab においてタイミング・エラー( 図2 )となってしまいました。

図1.乗算処理のモジュール

図2.タイミング・レポート

解決策としては

1.配線遅延( IC : Interconnect )を短縮する

2.レジスタ間のロジック・セル数( CELL )を少なくする

が考えられます。本コラムでは “2.レジスタ間のロジック・セル数( CELL )を少なくする” の方法をご紹介いたします!

パイプライン化

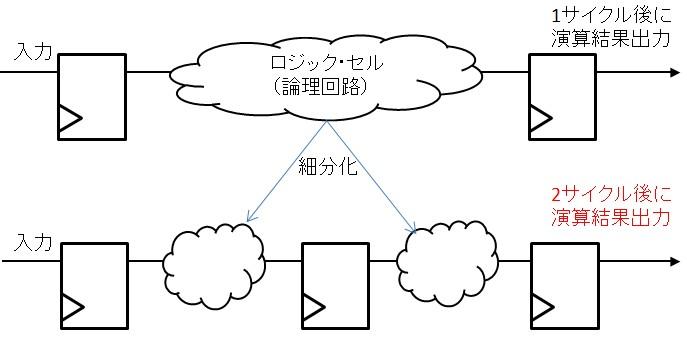

タイミング解析ツール TimeQuest は全ての送信レジスタと受信レジジスタの間のパスを解析しています。したがって、レジスタ間のロジック・セル数を少なくすることでデータ遅延を改善することができます。ロジック・セルの間にレジスタを挿入することを “パイプライン化” といいます( 図3 )。 ※ レジスタを挿入することでレジスタ間のロジック・セル数が減り、タイミングは向上しますが、レイテンシが増加します。下記図3では、2レイテンシ増加、つまり、2サイクル後に演算結果が出力されることになります。

図3.パイプライン化のイメージ

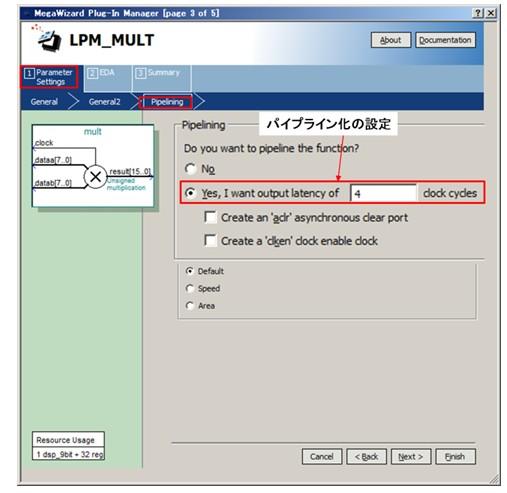

インテルで用意された MegaWizard の乗算器( LPM_MULT )にはパイプライン化のオプション設定がありました( 図4 )。 Output latency of “ 4 ” clock cycles に設定変更しました。

図4.LPM_MULTのパラメータ設定画面

演算処理(特に、乗算・割算演算)をハードウェア( FPGA )で実現するときはタイミングが厳しくなっていくことを考慮する必要があります。演算処理のビット数が増加すると、ベキ乗比例して回路規模が大きくなり、レジスタ間のロジック・セル数が増えるため、タイミングが厳しくなります( 図5 )。

図5.乗算器の RTL Viewer

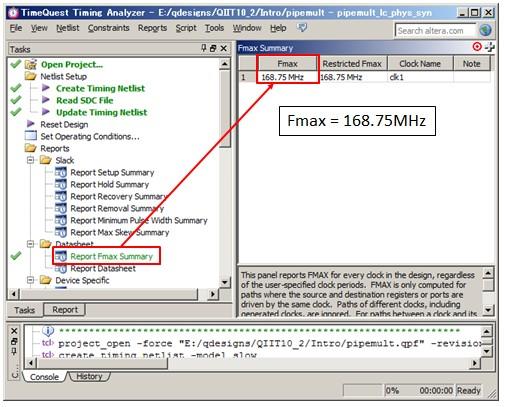

乗算器をパイプライン化したことで、最大動作周波数が 168.75MHz となり、希望する周波数 165.5MHz を満たすことができました。

| 学んだこと |

|---|

|