こんにちは、マス男です。

今週からスタートします、第二弾!『マス男の FPGA 実践シリーズ』

シリーズ第一弾は赤面エピソードをご紹介してきましたが、シリーズ第二弾からは FPGA 設計に役立つ情報をどんどん発信していきます!

第一回は、PLL ( Phase-Locked Loop )の位相調整を最適化する設計方法についてご紹介します。 PLL とはクロック信号を分周/逓倍、位相調整する回路です。PLL の詳しい説明は太郎先輩のコラム「 PLL の分周 / 逓倍(ていばい)」を参照下さい。

グローバル配線について

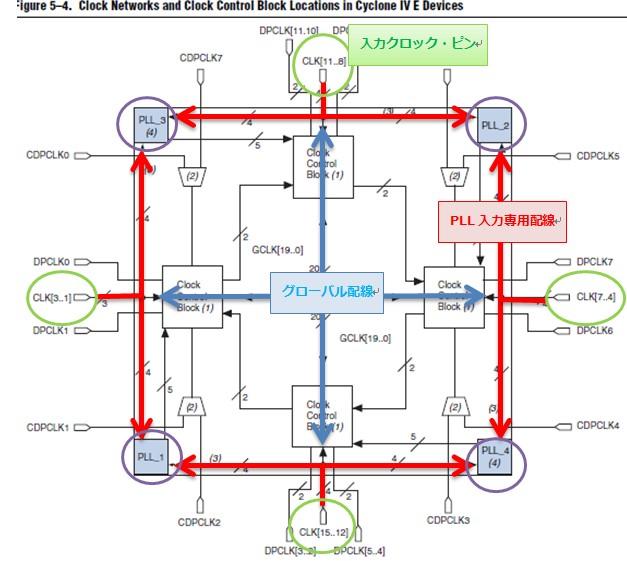

アルテラ社製 FPGA にはグローバル配線という Skew が “0” に近くなるように予め調整された専用の配線領域があります。クロック信号・リセット信号など、Fan-out が多い信号はグローバル配線にインプリメントするのが最適な設計となります。図1は Cyclone® IV E のグローバル配線アーキテクチャです。PLL の個数・グローバル配線の本数・配線アーキテクチャはデバイスによって異なりますので、該当するデバイスの Handbook でご確認下さい。本コラムでは Cyclone IV E を例にご紹介します。

図1. Cyclone® IV E のグローバル配線アーキテクチャ

Cyclone IV E はデバイスの四隅に PLL_1~4 が搭載されています。入力クロック・ピン(=CLK [*] )にピンアサインすることでグローバル配線にインプリメントされます。PLL をドライブする信号は CLK [*] にピン配置します。

PLL の位相調整を最適化する配置配線

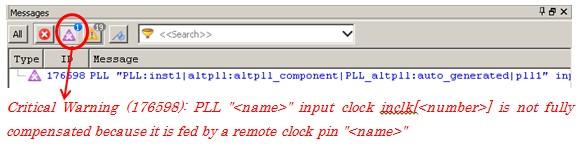

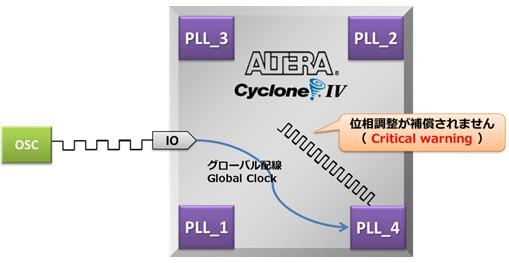

PLL をドライブする信号を CLK [*] にピン配置したとしても、使用される配線によって PLL の特長である位相調整が補償されないケースがあります。位相が補償されない配線を使用されると Fitter で Critical Warning ( 図2 )が発生します。

図2. 位相調整が補償されない Critical Warning

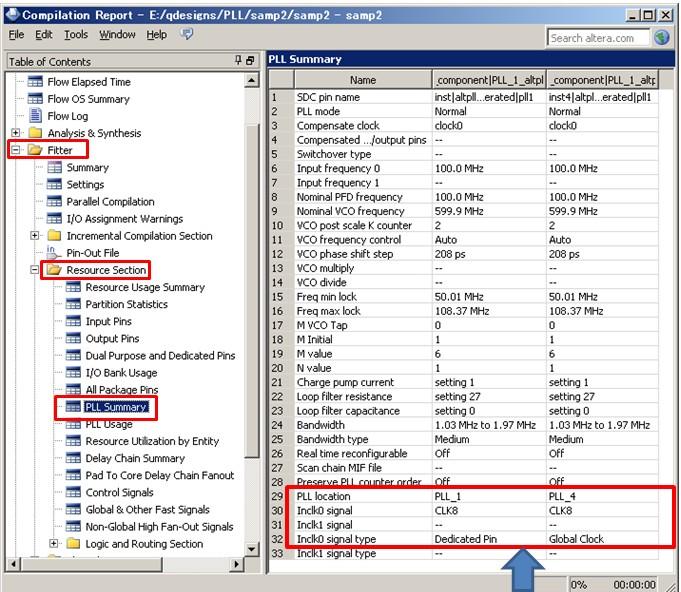

Fitter は CLK [*] の配置と PLL / 配線領域の使用率により、CLK [*] からの配線を自動選択します。よって配線については、ユーザが指定できるものではありません。配線結果はコンパイル・レポートの PLL Summary ( 図3 )で確認できます。

図3. PLL Summary コンパイル・レポート

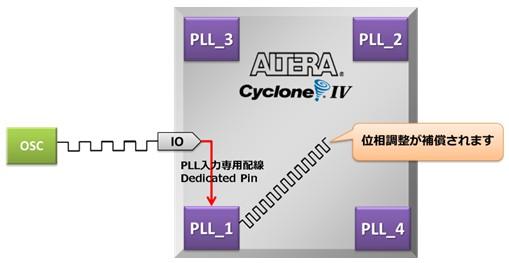

図3の PLL Summary で「 Dedicated Pin 」と表記された PLL_1 は位相調整が最適化されます( 図4 )。一方、「 Global Clock 」と表記された PLL_4 は位相調整が補償されません( 図5 )。

図4.PLL 位相調整が補償された配線のイメージ図

図5.PLL 位相調整が補償されない配線のイメージ図

配線はユーザが指定できるものではありません。しかし、「デザイン」と「ピン配置」を工夫することで、PLL 位相調整が補償される配線(= Dedicated Pin )に Fitter を誘導することは可能です。

| まとめ |

|---|

|

次回は、Dedicated Pin 配線に Fitter を誘導する方法をご紹介します。