こんにちは、マス男です。

“タイミング解析” について連載しております。新人研修で最も難しかったのが、タイミング解析の講義でした。本コラムでは、タイミング解析の講義資料やノートをまとめ、つまずいた点や有益な情報をご紹介したいと思います。

タイミング・エラーの原因は?

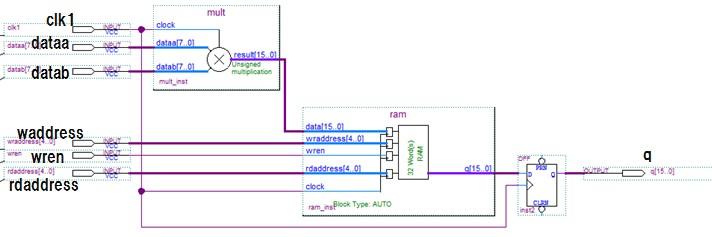

dataa [8bit] × datab [8bit] = q [16bit] の乗算器と RAM のモジュールを作成しました(図1)。

図1.乗算器と RAM のモジュール

動作周波数 165.5MHz で動作させたいと考えています。下記の通りに SDC ファイルにタイミング制約を与えました。

====================== SDC ファイル ===================================================

/*動作周波数 165.5MHz に制約*/

create_clock - period 6.042296073 - name clk1 [ get_ports { clk1 } ]

/*入力信号の最大/最小遅延値の制約*/

set_input_delay - clock { clk1 } - max 4.45 [ get_ports { data* } ] /* clk1 に同期する data が 最大で 4.45ns 遅れてFPGAに入力*/

set_input_delay - clock { clk1 } - min 1.75 [ get_ports { data* } ] /* clk1 に同期する data が 最小で 1.75ns 遅れてFPGAに入力*/

set_input_delay - clock { clk1 } - max 2.5 [ get_ports { rdaddress* wraddress* } ]

set_input_delay - clock { clk1 } - min 1.0 [ get_ports { rdaddress* wraddress* } ]

set_input_delay - clock { clk1 } - max 2.5 [ get_ports { wren } ]

set_input_delay - clock { clk1 } - min 1.0 [ get_ports { wren } ]

/*出力信号の最大/最小遅延値の制約*/

set_output_delay - clock { clk1 } - max 0.7 [ get_ports { q* } ]

set_output_delay - clock { clk1 } - min 0.0 [ get_ports { q* } ]

======================================================================================

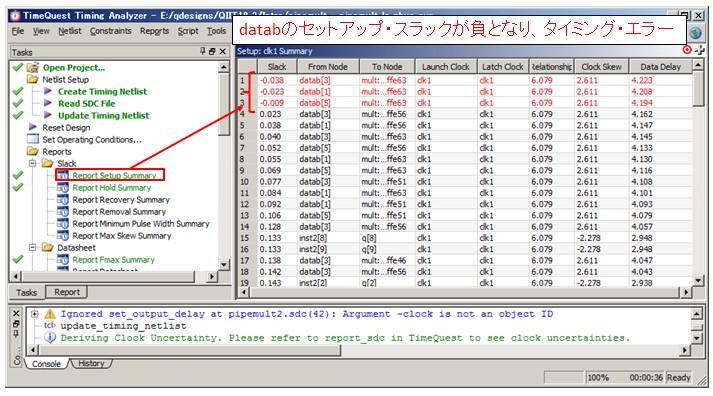

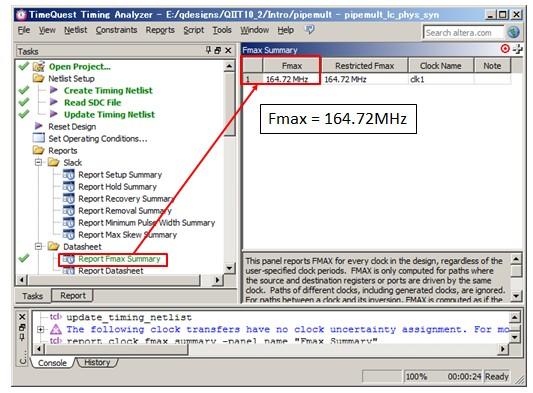

コンパイルを実行し、タイミング・レポートを確認したところ、タイミング・エラーとなっていました( 図2 )。詳しく見ると、datab がセットアップ違反になっていました。つまり、受信エッジに対して datab の到着が遅いことが分かります。理想は 165.5MHz で動作させたいが、現実は 164.72MHz が最大動作周波数でした。

図2.タイミング・レポート

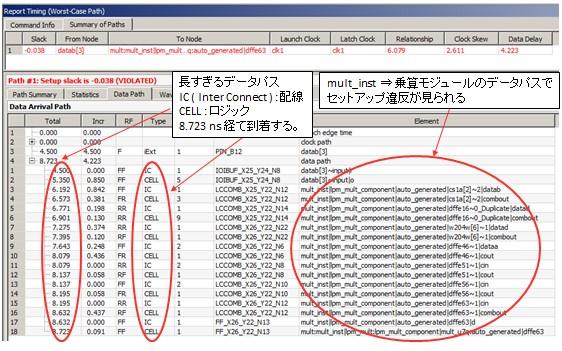

タイミング・エラーの原因を詳しく見ると、乗算器モジュールにおいて “長すぎるデータパス” に原因がありました( 図3 )。

図3.データパスの到着時間詳細レポート

解決策としては

1.配線遅延( IC : Interconnect )を短縮する

2.レジスタ間のロジック・セル数( CELL )を少なくする

が考えられます。

本コラムでは “1.配線遅延( IC )を短縮する” の方法をご紹介いたします!

パフォーマンスを最適化するコンパイル・オプション

インテル® Quartus® Prime 開発ソフトウェア では、パフォーマンスを最適化するためのコンパイル・オプションがあります。これにより、最適な配置配線を行うことで IC 遅延を短縮することができます。

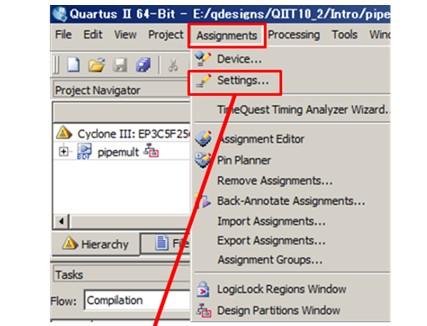

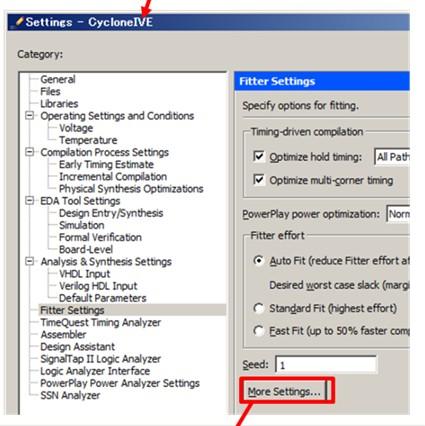

Assignments メニュー > Settings > Fitter Settings > More Settings … の順にクリックします。 Router Timing Optimization Level 欄を “Maximum” に設定すれば OKです( 図4 )。

Router Timing Optimization Level は、オプション名の通り、タイミング制約を満足するように配線の最適化を行う度合いを指定します。 Maximum にすることで配線の最適化を最大限行う指定です。( オプション設定により、タイミング制約を全て満足できるという保証ではありません )

図4.Router Timing Optimization Level の設定

続いて

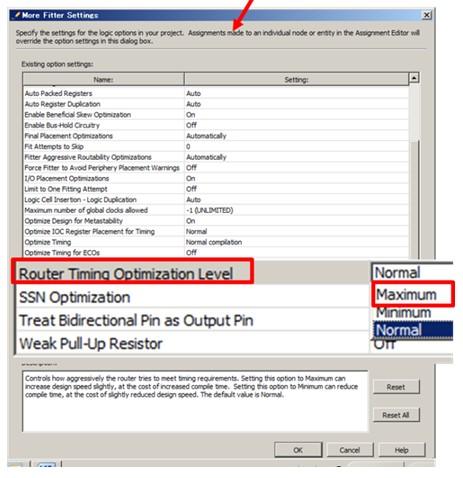

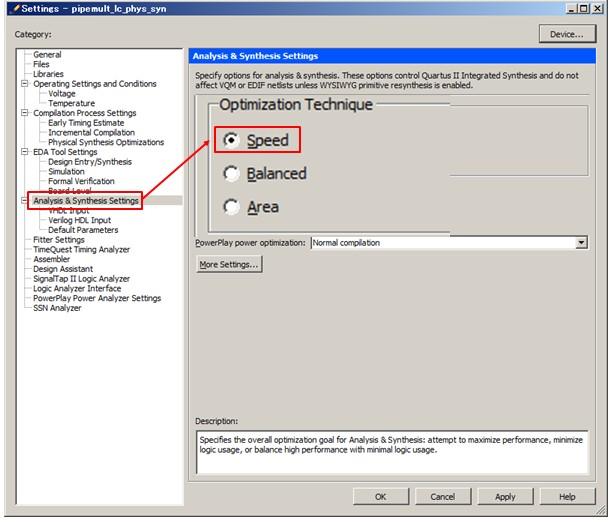

Assignments メニュー > Settings > Analysis & Synthesis をクリックします。Optimization Technique 欄を “Speed” に設定すれば OK です( 図5 )。

Otimization Technique は、論理合成時に何を重要視した論理合成を行うかを指定します。Speed を選択することで速度重視の論理合成を行うように指定しました。

図5.Optimization Technique 設定

上記2つの設定を行い、再度コンパイルしました。

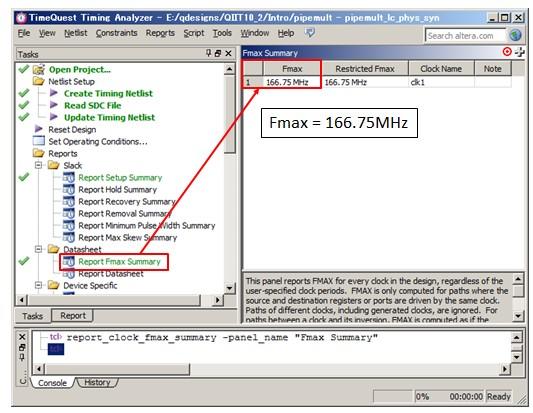

図6. 最適化したコンパイル・レポート結果

パフォーマンスを最適化するコンパイル・オプションを使用したことで、最大動作周波数が 166.75MHz となり、希望する周波数 165.5MHz を満たすことができました。

| まとめ |

|---|

|

次回は “2.レジスタ間のロジック・セル数( CELL )を少なくする” により、タイミングを満たす方法をご紹介いたします。