こんにちは、マス男です。

今週から “タイミング解析” について連載していきます。新人研修で最も難しかったのが、タイミング解析の講義でした。本コラムを通して、タイミング解析の講義資料やノートをまとめ、つまずいた点をご紹介したいと思います。

本日は SDC コマンドについて。こちらは TimeQuest の SDC 記述の例です。

様々な SDC 記述がありますが、本コラムでは新人研修でピックアップされた SDC 記述をご紹介したいと思います。

クロック制約

表1.クロック制約の SDC コマンド一覧.

|

コマンド |

内容 |

|---|---|

| create_clock | クロックピンから供給されるクロック周波数を定義。 |

| create_generated_clock | 内部ロジック/ PLL から供給されるクロック周波数を定義。 |

| derive_pll_clocks | 内部 PLL から供給されるクロック周波数を定義。 PLL 全ての出力を制約できる便利なコマンド。 |

| set_clock_uncertainty | クロックの立ち上がり/下がり時間のばらつきを定義。ユーザ自身が基板に即した制約ができる。 |

| derive_clock_uncertainty | クロックの立ち上がり/下がり時間のばらつきを定義。アルテラが用意したばらつきモデル。 |

| set_clock_latency | 外部デバイスと FPGA 間のクロック遅延時間を定義。 |

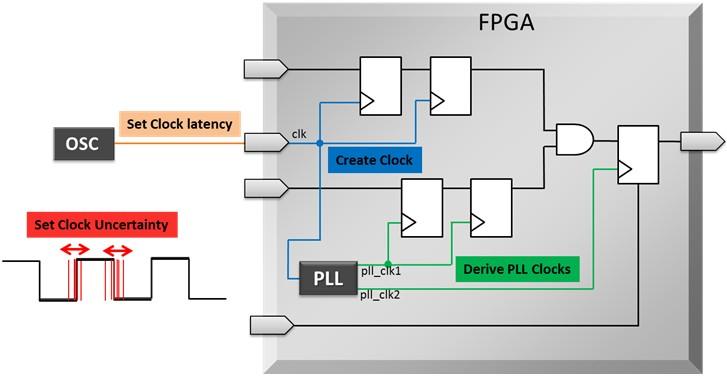

各コマンドによるクロック制約の様子を 図1 でイメージしました。

図1.クロック制約のイメージ

I/O 制約

表2.I/O 制約の SDC コマンド一覧.

|

コマンド |

内容 |

|---|---|

| set_input_delay | 入力信号の遅延時間を定義。 |

| set_output_delay | 出力信号の遅延時間を定義。 |

| set_false_path | 指定したパスをタイミング解析から除外する。非同期パス(リセット/クリア信号)等に使用。 |

| set_multicycle_path | セットアップ/ホールドのそれぞれについて、任意のクロックエッジでの解析を定義。 |

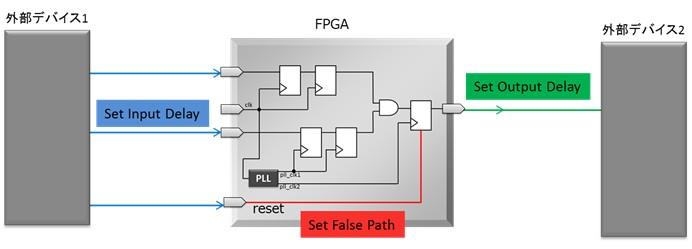

各コマンドによる I/O 制約の様子を 図2 でイメージしました。

図2. I/O制約のイメージ

このように、TimeQuest Timing Analyzer は外部デバイスと FPGA の関係も考慮して解析します。 FPGA で Close するのではなく、基板全体のタイミング解析をしているのです!

| まとめ |

|---|

|