【第 5 回】 これが究極の低消費電力手法?

低消費電力設計手法は細かな対策の積み重ねです。

細かな対策を覚えることよりも、消費電力計算式とそこに使われているパラメーターを理解して、普段から消費電力を意識した設計が重要です。

今まで、計算式を理解するのは面倒と思っていた方も、一度はじっくりと計算式を見ることをお勧めします。

自分の知っている低消費電力手法がどのパラメーターに影響しているかを見ると理解を早めることができると思います。

1.1 CMOS回路の消費電力計算式

| 消費電力 | = | ダイナミック電力 + リーク電力 |

| = | [スイッチング電力 + ショートサーキット電力]+ リーク電力 | |

| = | [0.5*(C*Vs*VCC*F)*N] + [Q*VCC*F*N] + [(Idc+Ileak)*VCC] |

| C:負荷容量 |

| Vs:信号振幅 |

| VCC:電源電圧 |

| F:動作周波数 |

| N:信号遷移頻度(トグル率) |

| Q:貫通電流による電荷 |

| Idc:回路固有のDC電流 |

| Ileak:リーク電流 |

1.1.1 ダイナミック電力

信号が遷移した時の電力で、スイッチング電力とショートサーキット(貫通)電力の合計です。

(1) スイッチング電力

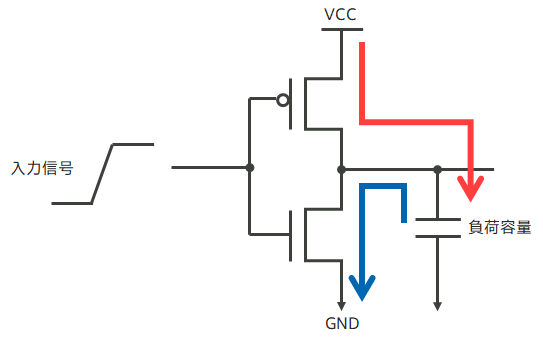

セルが動作して、負荷容量を充放電した際に消費する電力の事です。

負荷容量は、配線容量と次のセルの入力ピン容量の合計です。

例えば、インバーターの入力に ”L” を入力すると pMOS が ”ON”、nMOS が ”OFF” になり、VCC から電流が流れて、配線や次段の入力ピンの容量を充電します。この時に pMOS の抵抗により電力を消費します。

次に、インバーターの入力に ”H” を入れると pMOS が “OFF”、nMOS が ”ON” になり、負荷容量に充電された電荷が nMOS を通って GND へ流れます。この時に nMOS の抵抗により電力を消費します。

この容量は、配線抵抗と次段セルの入力ピン容量の合計となり、配線が長く Fanout が大きいとスイッチング電力が増加します。

(2) ショートサーキット電力

CMOS は入力信号が ”L” か ”H” で安定していれば、pMOS か nMOS のどちらかが必ず OFF になり、リーク電流を除き VCC から GND へ電流が流れません。

CMOS が低消費電力と言われてる理由です。しかし、入力信号の立上りや立下りが鈍いと、一時的に pMOS と nMOS が両方共に少し開いた ON 状態になります。

この時に、VCC から GND へショートサーキット電流が流れ、この電力をショートサーキット電力と言います。

1.1.2 リーク電力

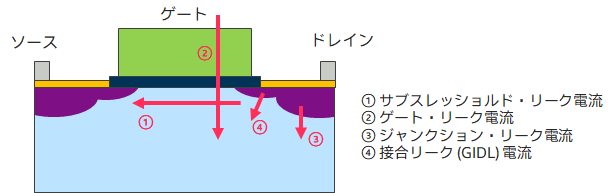

下記の4種類のリーク電流によって通じる電力がリーク電力です。

古いプロセスでは無視できる程に小さな値でしたが、最新プロセスではかなりリーク電力が大きくなりました。

これらのリーク電力はトランジスターに電圧が掛かっていれば動作に関係なく消費します。

現在では、サブスレッショルドリーク電流とゲート・リーク電流が大半です。

サブスレッショルドリーク電流は温度依存性が高いので、高温になると更にリーク電力が増します。

|

種 類 |

内 容 |

原 因 |

温度 依存性 |

| サブスレッショルドリーク電流 (ソース-ドレイン・リーク) |

トランジスタがOFF状態でソースとドレイン間に流れる電流 | トランジスタのVt(閾値電圧)低下 |

大 |

| ゲート・リーク電流 | トンネル効果により、 ゲートからゲート酸化膜を通ってソースへ流れる電流 |

ゲート酸化膜の薄膜化 |

小 |

| ジャンクション・リーク 電流 | ソース、ドレインと基板間に流れる電流 | 不純物の濃度増大や 素子の結晶欠陥など |

小 |

| 接合リーク(GIDL)電流 | ゲート-ドレイン間の電界による電流 | ゲート酸化膜の薄膜化 |

小 |

表 1.各リーク電流の比較

次回より、各パラメーターを低減する具体的な方法をご紹介します。