インテル® FPGA では、JESD204B IP コアを使用することで、JESD204Bインタフェースを実現させることができます。本記事では、インテル® Quartus® Prime 開発ソフトウェアを使用して JESD204B のループバック・サンプル・デザインを生成し、Arria® 10 GX FPGA 開発キットにて動作確認するまでの一連の流れを説明します。

インテル® FPGA における JESD204B インタフェースの詳細については、こちらを参照してください。

インテル® FPGA JESD204B IP (インテル)

本記事は、以下の資料を参考に作成しましたので、以下も合わせてご参照ください。

Arria 10 JESD204B IP コアのサンプル・デザインのユーザ・ガイド (インテル)

JESD204B IP コアのユーザ・ガイド (インテル)

環境

- ツール:インテル® Quartus® Prime 開発ソフトウェア v17.0

- 開発キット:インテル® Arria® 10 GX FPGA 開発キット <Macnica-Mouser 購入サイト>

手順

- サンプル・デザインの作成

- デザイン構成の確認

- 動作確認

- まとめ

- 参考情報

1. サンプル・デザインの作成

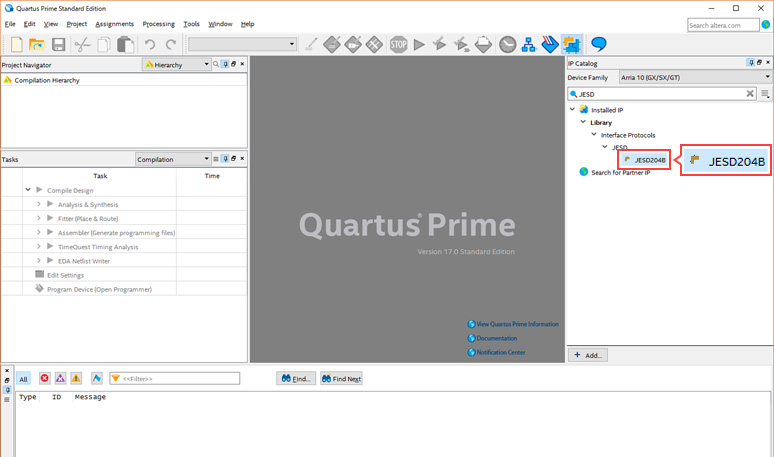

まず、Quartus® Prime を起動し、IP Catalog から Device Family を Arria 10 に設定し、検索ボックスに JESD と入力します。

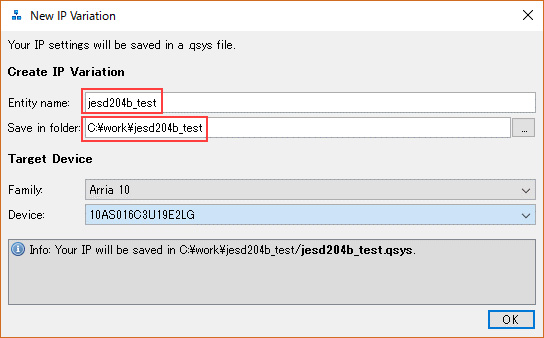

JESD204B をダブルクリックして Qsys を起動します。New IP Variation が表示されるので、Entity Name を適当に入力します。ここでは、jesd204b_test としました。また、Save in folder に、サンプル・デザインを生成するフォルダを指定します。ここでは、c:\work\jesd204b_test としました。

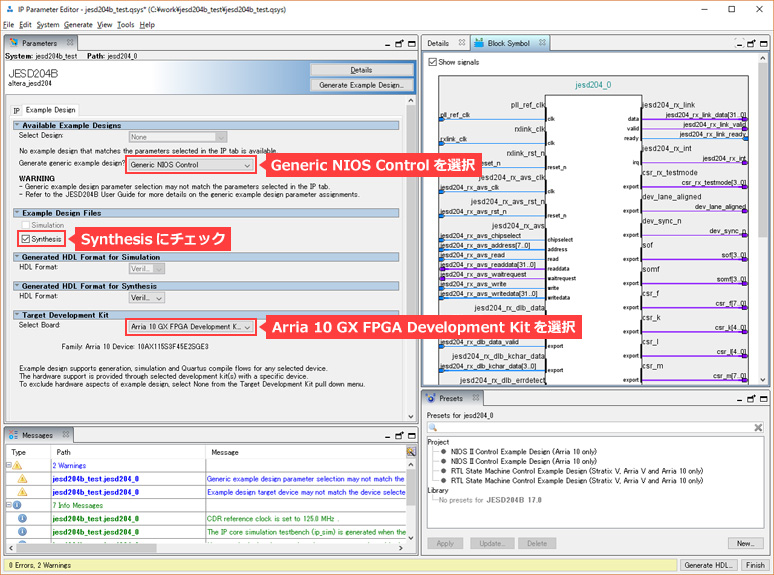

OK ボタンをクリックすると、Qsys ファイルが保存されます。Qsys 画面は、以下のようになっています。ここでは、サンプル・デザインを生成するので、Example Design タブを選択します。実機での動作確認を行うため、以下の3項目を設定して、画面の上の方にある Generate Example Design ボタンをクリックします。(右下の Generate HDL ではありません。)

- Generate generic example design? ⇒ Generic NIOS Control を選択

- Example Design Files ⇒ Synthesis にチェック

- Select Board ⇒ Arria 10 GX FPGA Development Kit を選択

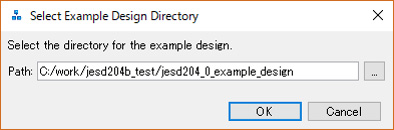

ファイルの保存場所を求められるので、保存したいフォルダを指定して OK ボタンをクリックします。

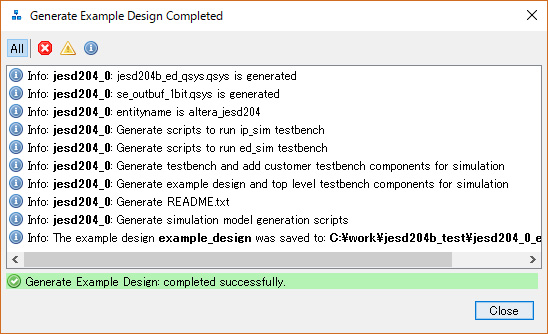

サンプル・デザインが生成されます。

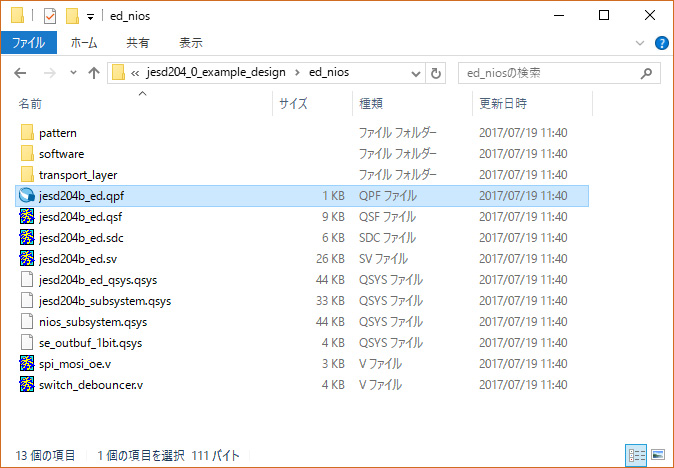

生成された ed_nios フォルダの内容は、以下のようになっています。

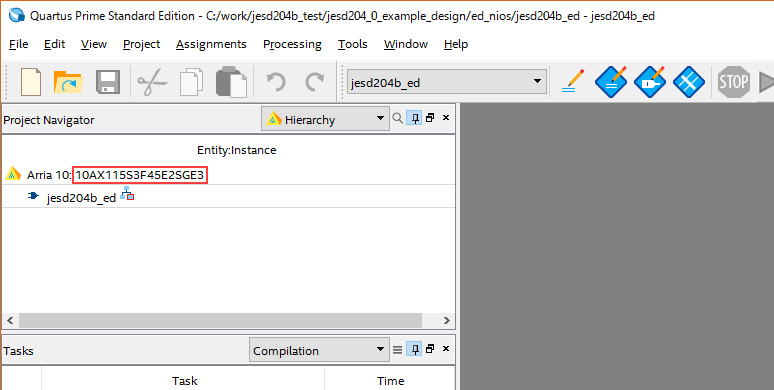

Quartus® Prime の File メニュー ⇒ Open Project から、jesd204b_ed.qpf を選択して、生成されたプロジェクトを開きます。Arria® 10 GX Development Kit のデバイスが予め設定されています。Quartus® Prime v17.0 では、ES3 品の型番となっておりますが、プロダクション品と SOF 互換なのでそのまま進めても、プロダクション品の型番に手動で変更しても、どちらでも構いません。ここでは、そのまま進めます。

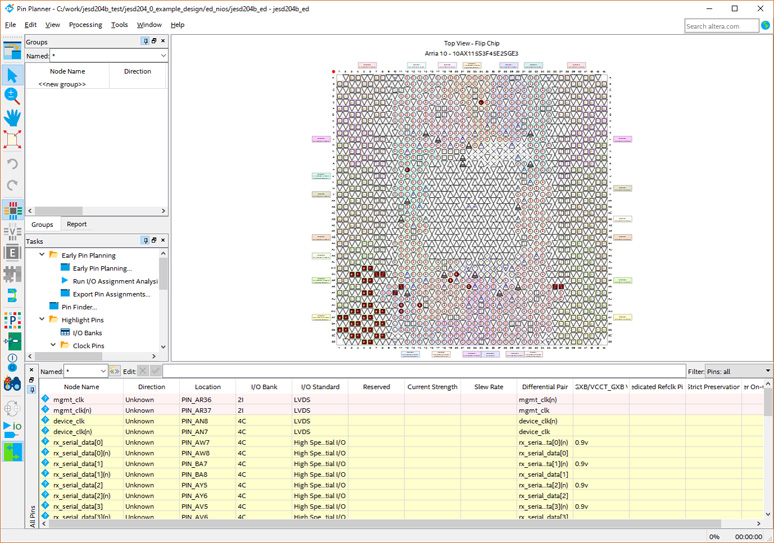

Quartus® Prime の Pin Planner を開くと、既に必要なピン・アサインがされていることが確認できます。

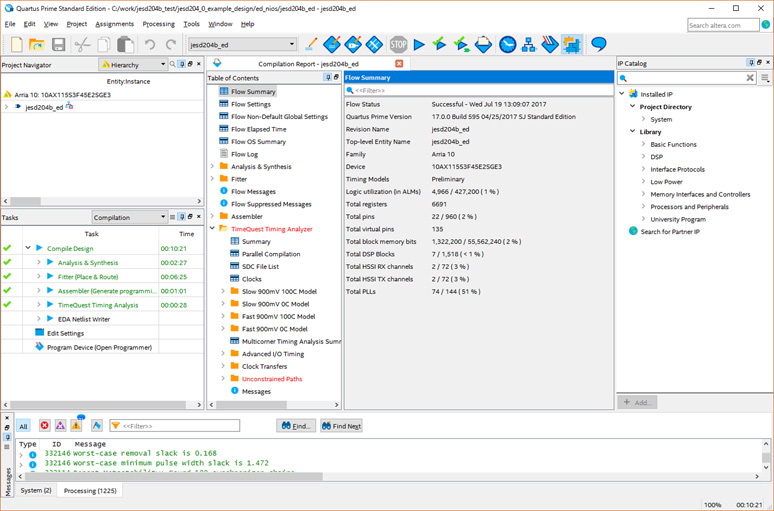

デザインをコンパイルします。Processing メニューの Start Compilation を実行してください。コンパイルが完了すると、以下のようになります。

2. デザイン構成の確認

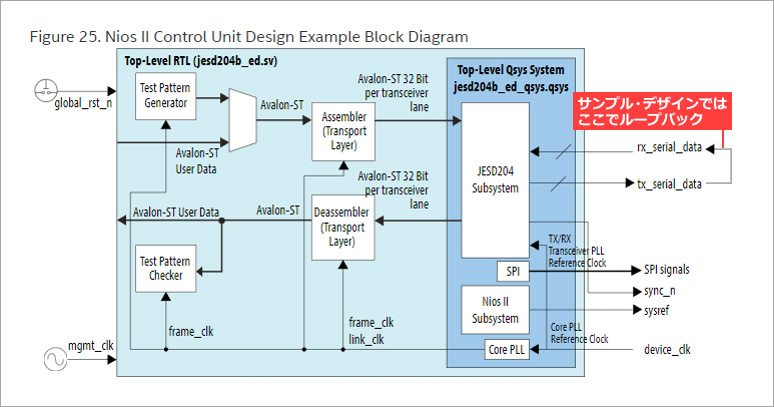

自動生成されるサンプル・デザインの構成は、以下となります。

- レーン数(L):2レーン

- コンバータ・デバイス内のコンバータ数(M):2

- 1フレーム内のオクテット数(F):2

- レーン・レート:6.144Gbps/Lane

- Device Clock:153.6MHz

- Nios II ベース・デザイン

- FPGA デバイス内でのシリアル・ループバック、または、FMC ポート A で外部ループバック

下図がサンプル・デザインのブロック・ダイアグラムとなります。本サンプル・デザインは、FPGA 内でのJESD204B IP コアの検証用であるため、FPGA デバイス内でのシリアル・ループバック、または、FMC ポート A での外部ループバックで PRBS データの送受信を行い正しくデータが疎通していることを確認することを目的としています。デバイス内の各コンポーネントの初期化、Test Pattern Generator/Checker の制御、sysref の送出などの処理は、Nios II のソフトウェアが行います。

詳細については、Arria 10 JESD204B IP Core のサンプル・デザインのユーザ・ガイド を参照してください。

3. 動作確認

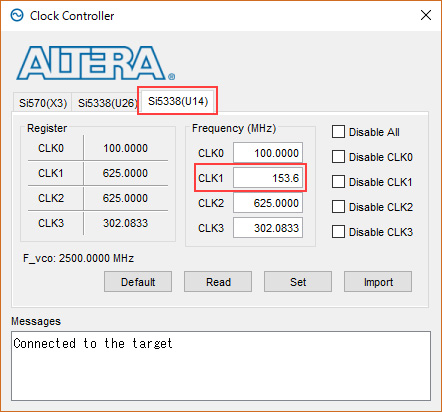

まず、ハードウェアの設定を行います。Arria® 10 FPGA 開発キットに JTAG ケーブルと電源ケーブルを接続し、電源を入れます。キットに付属の ClockControl.exe を実行し、SI5338(U14) の CLK1 を 153.6MHz に設定します。

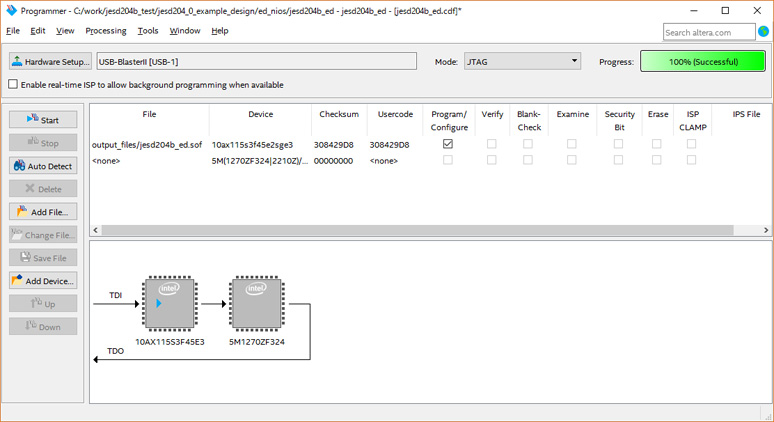

Programmer を起動して、 SOF ファイルを書き込みます。

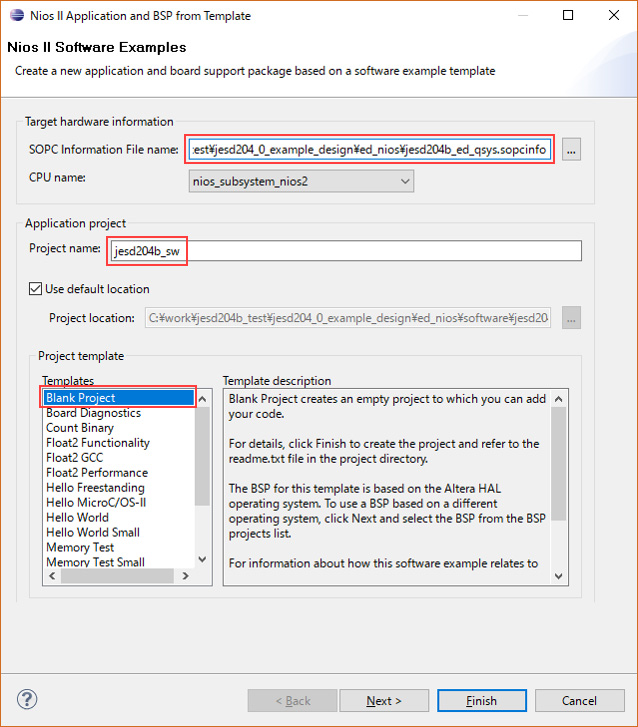

software フォルダ内の C 言語ソース・コードを使用して、Nios® II 用のソフトウェアを作成します。Nios® II software Build Tools for Eclipse(以下、Nios® II SBT) を起動して、以下のように設定します。プロジェクト名は任意ですが、ここでは、jesd204b_sw と入力します。Finish をクリックしてソフトウェア・プロジェクトを作成します。

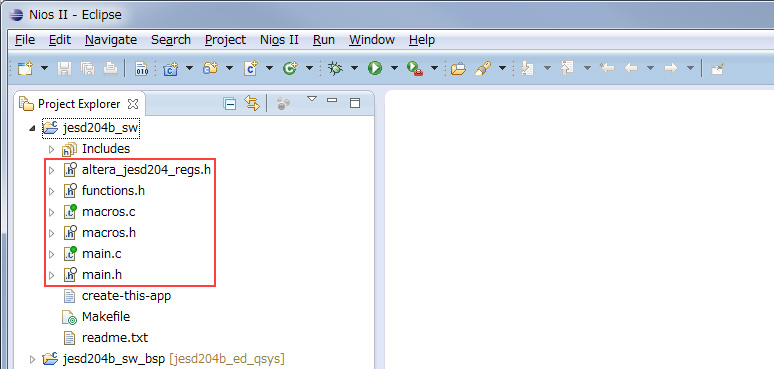

source フォルダ内のソース・ファイルを Nios® II SBT にインポートします。

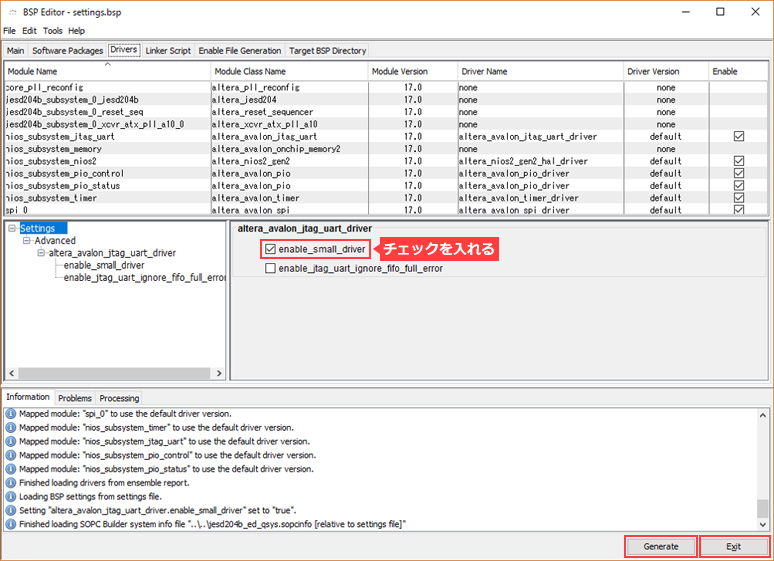

BSP Editor を起動します(jesd204b_sw_bsp プロジェクトを右クリック ⇒ Nios II ⇒ BSP Editor )。Drivers タブの altera_avalon_jtag_uart_driver の enable_small_driver にチェックを入れます。この設定は、JTAG UARTからの割り込み信号を無視して動作する設定となります。設定したら、Generate ボタン、Exit ボタンの順でクリックし、BSP Editor を閉じます。

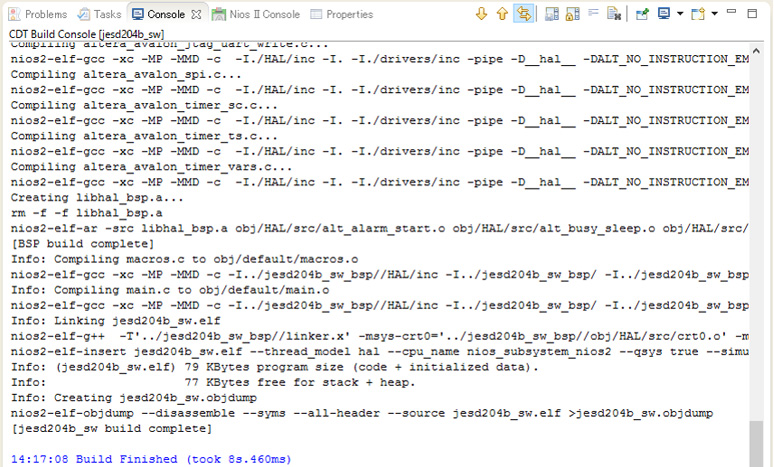

ソフトウェアをビルドします(jesd204b_sw プロジェクトを右クリック ⇒ Build Project )。正常に終わると、以下のようになります。

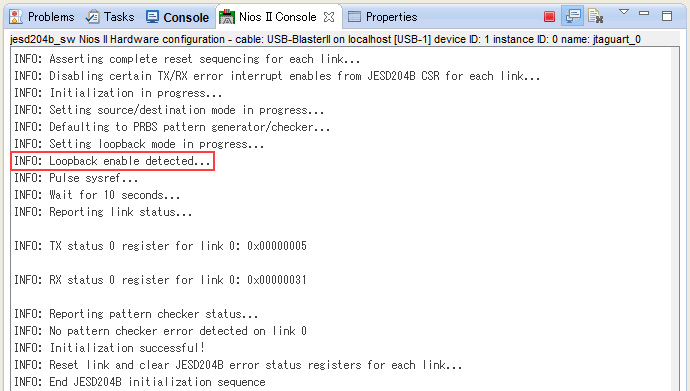

Nios® II ソフトウェアを実行します(jesd204b_sw プロジェクトを右クリック ⇒ Run As ⇒ Nios II Hardware)。正常に実行されると、以下のように Nios II Console に実行ログが表示されます。

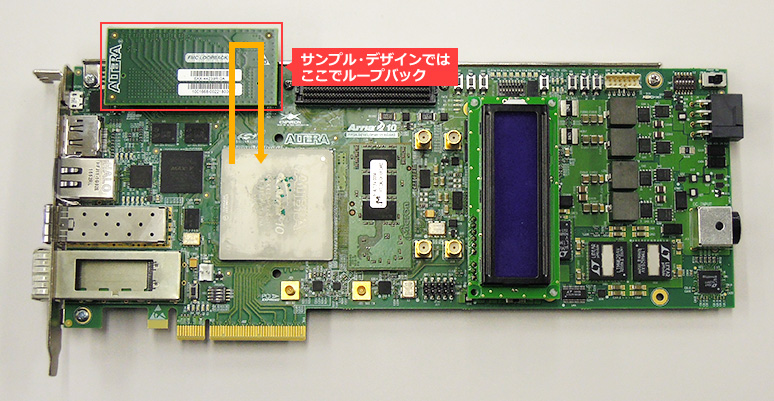

ソフトウェアの初期の状態では、FPGA デバイス内でのシリアル・ループバック設定となっています。ソフトウェアの設定を変えることで、FMC ポート A で外部ループバックの設定に変更可能です。以下のようにFMC ポート A に付属の FMC Loopback コネクタを実装します。

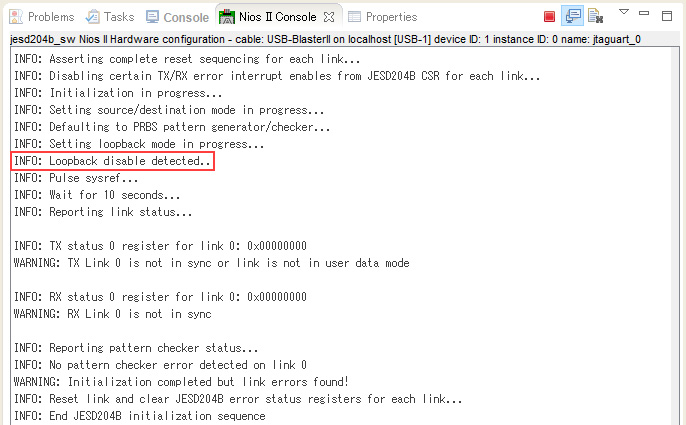

main.h を以下のように編集し、Nios® II ソフトウェアを再ビルドします。再ビルドが完了したら、Nios® II ソフトウェアを実行します(jesd204b_sw プロジェクトを右クリック ⇒ Run As ⇒ Nios II Hardware)。

編集前

#define LOOPBACK_INIT 1

編集後

#define LOOPBACK_INIT 0

実行後のログを見ると、Loopback に関するメッセージが以下のようになっていることが確認できます。

INFO: Loopback disable detected...

ちなみに、FPGA デバイス内でのシリアル・ループバックの場合、以下のように表示されます

INFO: Loopback enable detected...

4. まとめ

ここまでの作業で、FPGA 内にJESD204B IP コアを実装した状態での高速シリアル通信が確認できました。次のステップは、実際に、ご使用になるDAコンバータ(FPGA からみて送信側)、または、ADコンバータ(FPGA からみて受信側)の評価用ボードを実装した通信の確立となります。簡単にまとめると、以下の実装が必要となります。

- クロック関連の接続(Device Clock、sysref、sync_n、など)

使用する AD/DA コンバータ評価用ボードによって仕様が異なるため、詳細を理解した上での実装が必要です。

- SPI 等のインタフェースを使用した DA/AD コンバータ・デバイスへのレジスタ設定の実装

紹介したデザインでは、SPI のインタフェースが標準で実装されているので、使用する AD/DA コンバータ評価用ボードが SPI 対応であれば正しく配線をして、ソフトウェアからの制御部分を実装することで比較的容易に実現が可能です。

また、初めに紹介した以下のページより、実際にインテル社で接続テストを行ったリファレンス・デザインがダウンロードできますので、実装の参考としてご参照ください。

Intel® FPGA JESD204B IPページ

5. 参考情報

インテル® FPGA では、いくつかの代表的な AD/DA 評価用ボードとの通信テストを実際に行いチェックアウト・レポートという形で公開しています。以下は、比較的新しいリリースとなります。

AN 710: Altera JESD204B MegaCore Function and ADI AD9680 Hardware Checkout Report

AN 712: Altera JESD204B MegaCore Function and ADI AD9625 Hardware Checkout Report

AN 719: Altera JESD204B IP Core and TI DAC37J84 Hardware Checkout Report

AN 733: Altera JESD204B IP Core and TI ADC12J4000 Hardware Checkout Report

AN 749: Altera JESD204B IP Core and ADI AD9144 Hardware Checkout Report

AN 753: Altera JESD204B IP Core and ADI AD6676 Hardware Checkout Report

AN 779: Altera JESD204B IP Core and ADI AD9691 Hardware Checkout Report

AN 810: Intel JESD204B IP Core and ADI AD9208 Hardware Checkout Report

AN-785: Altera JESD204B IP Core and ADI AD9162 Hardware Checkout Report

AN-792: Intel JESD204B IP Core and ADI AD9371 Hardware Checkout Report

おすすめ記事/資料はこちら

IP 関連の記事や資料 はこちら...