こんにちは。マクニカでインテル® FPGA 製品の技術サポートをしている鷲宮タローです。

今回は、FPGA と次世代 CMOS イメージ・センサをつなぐ新しいインタフェース規格についての話です。日々の商談から、イメージ・センサを使った開発案件がどんどん増えているなぁ、と実感している昨今です。私が担当している FPGA はイメージ・センサとの接続に使われることが多いので、そのアプリや関連技術については常にアンテナを高くしています。

このたび、マクニカの開発部門にて、最先端のインタフェースとその Intellectual Property (IP) について学んできましたので、皆さんに紹介したいと思います。

はじめに

CMOS イメージ・センサで大きなシェアを持つソニーが、次世代高解像度 CMOS イメージ・センサに適した新しいインタフェース「SLVS-EC 規格」を策定しました。そのインタフェースを備えたイメージ・センサの製品化も強力に進められています。

マクニカは、いち早くその新しいインタフェースに着目し、FPGA に容易に接続するための「SLVS-EC Rx IP」を開発、お客様への提供を開始しました。昨年、ドイツで開催された Vision 2016 ではそのデモンストレーションを行っています。

なぜ今、新しいインタフェース?

現在、イメージ・センサのインタフェースは LVDS (Low Voltage Differential Signaling) と呼ばれる低振幅差動インタフェースが主流です。コモン・モード・ノイズに強く、低振幅で高速にデータ転送ができるため、広い用途で使われています。

ただ、ますます高速化や高解像度化が進むイメージ・センサでは、大量のイメージ・データをより高速に、より低消費電力でというニーズが増加しています。LVDS は差動信号ペア 1レーンで約 600 Mbit/sec で送れますが、FPGA との接続では、8、16、32レーン、いやそれ以上も、というセンサ・ニーズが出てきています。LVDS は広く使いこなされている技術ですが、接続には全レーン間のスキューを正確に抑え込まねばならず、レーン数が増えれば増えるほど基板設計が困難になっています。従って「基板設計をなんとかしたい」というニーズも強まる一方です。

ソニーの「SLVS-EC規格」って?

Scalable Low Voltage Signaling Embedded Clock の略からのネーミングです。ネーミングから LVDS 同様の低振幅差動インタフェースで、高ノイズ耐性をそのまま受け継ぎ、更に低振幅・低電力で、クロック埋め込み型であることが大きなアドバンテージということです。

LVDS では、クロックがデータとは別のレーンで送る仕様のため、前出の基板設計が困難になるという問題が顕在化していますが、SLVS-EC ではイメージ・センサ側(送信側)でクロックをデータに重畳して送り、FPGA 側(受信側)でクロックを再生する方式のため、基板設計が容易になり、より高速に、より遠くまでデータを送ることができます。

更にソニーは、イメージ・センサに適用するインタフェースとして、上記「物理層」での特徴に加えて、初期化やモード変更など「リンク層」を定義・規格化していますので、ユーザにとってより使い易いインタフェースになっています。

「SLVS-EC Rx IP」で簡単接続!

リンク層を含む規格ですので、専用のインタフェース回路が IP になっていると更に使い易いです。マクニカが受信用に開発した「SLVS-EC Rx IP」を使えば、規格を深く知らなくても容易に SLVS-EC インタフェースをつなげられるでしょう。

ここでSLVS-EC Rx IP の特長および概略仕様を示しておきます。

特長

- SLVS-EC Specification Version 1.2 対応

- SLVS-EC Link 層で定義される各種機能を実現(物理層は Altera PCS/PMA で実現)

- 各種レーン構成に於ける Byte to Pixel 変換をサポート

- ヘッダ解析とペイロード・エラー検出機能を搭載

概略仕様

| 機 能 | 諸 元 |

| Transfer Rate | 2.3 Gbps/Lane |

| Clock | Embedded Clock (8b/10b Encoding) |

| Number of Lanes | 1, 2, 4, 6, 8 |

| Baud Grade | 1, 2 |

| Bit per Pixel | 8, 10, 12, 14 |

| CRC | Limited※ |

| ECC | Supported |

| Embedded Data | Supported |

| Dynamic Mode Change | Supported |

| Multiple Stream | Optional |

※使用する FPGA や構成により動作周波数を満たせない場合あり

デモンストレーションはどんなもの?

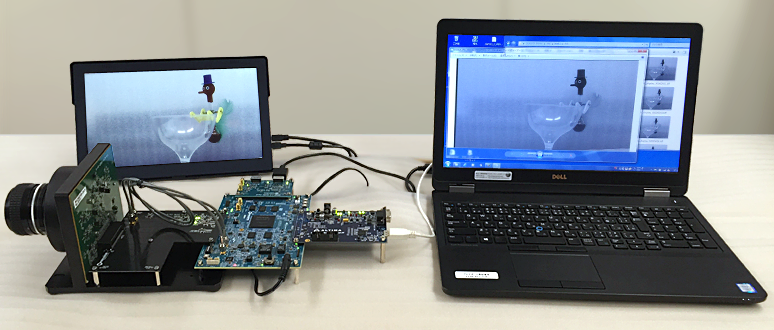

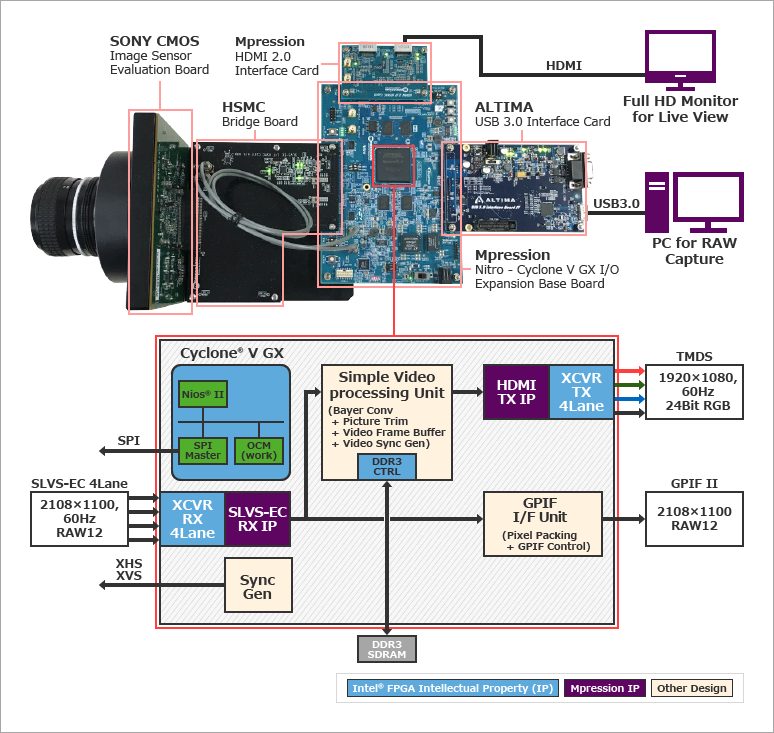

やはり新しいものは実動している様子を見るのと見ないのとでは印象に格段の違いがあります。今回見せてもらったデモは、ソニー製 CMOS イメージ・センサ評価ボードを使用し、マクニカの持つ資産を組み合わせて実現したとのことです。

イメージ・センサで受けた画像データを 4レーンの SLVS-EC インタフェースを経由して FPGA 開発キット「Nitro」に転送、そして FPGA 内で 2つの出力パスに分配、一方は HDMI インタフェースを介して HD モニタにライブ映像を表示、もう一方は USB3.0 インタフェースを介して PC に RAW イメージ・データを出力するものです。もちろんですが、SLVS-EC インタフェースがきちんと稼働している様子がわかりました。言葉では分かりにくいので、デモの処理フローがわかる接続の様子を写真とブロック図で示します。

このデモ・セットはあいにく販売されていませんが、「SLVS-EC Rx IP」は元よりこのデモで使った IP やボードはマクニカから単品販売されていますので、容易に同様の環境が構築できると思います。もちろん一番重要なイメージャの部分は、ソニー様にお願いしていただく必要がありますが...

以上、鷲宮タローの最新技術レポートでした。

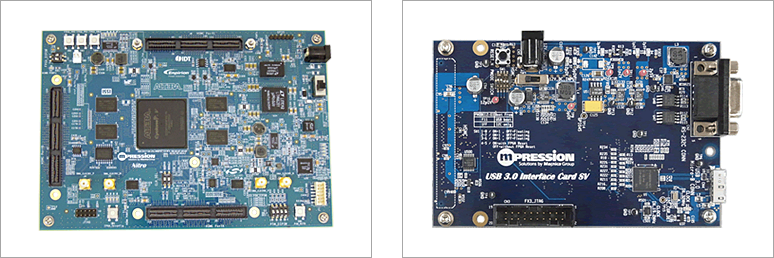

マクニカより提供可能なIPやボード

SLVS-EC Rx IP

HDMI 2.0 Tx IP

Nitro Cyclone V GX I/O 拡張ベースボード ALTNITROC5GX

USB 3.0 インタフェース・ボード ALTHSMCUSB3SV

紹介した IP やボード製品に興味がある方は、下記へご連絡ください。

商品の購入はこちら

Nitro Cyclone V GX I/O 拡張ベースボード ALTNITROC5GX

USB 3.0 インタフェース・ボード ALTHSMCUSB3SV