こんにちは。

マクニカでインテル® FPGA 製品の技術サポートをしている インテル・F・ハナコ です。

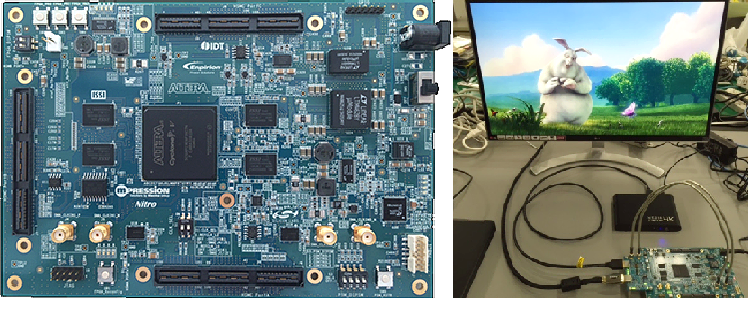

Mpression 製 HDMI 2.0 IP を FPGA に実装して、4K動画を映すデモを体験してきました!!

今回のデモで使用した FPGA は、インテル® FPGA の Cyclone® V GX !!

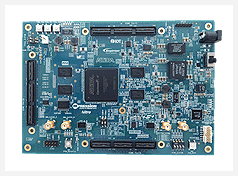

その FPGA が搭載された Mpression 製の Nitro(ニトロ)- Cyclone® V GX I/O 拡張ベースボード (現在は製造終了) を使いました。

なぜ Nitro ボードにしたかと言えば、大半の I/O 端子を拡張コネクタ(HSMC)にユーザー I/O として接続しているので色んなタイプのドータカードを合わせることができるので、検証の自由度があるんです。

ここで、HDMI 規格の各バージョンの基本性能をおさらいします。

| Table 1: HDMI 規格の各バージョンの基本性能 | ||||||

| HDMI バージョン |

1 | 1.1 | 1.2 | 1.3 | 1.4 | 2 |

| 最大伝送速度 | 4.95 Gbps | 4.95 Gbps | 4.95 Gbps | 10.2 Gbps | 10.2 Gbps | 18 Gbps |

| 最大解像度 (フレームレート) |

1920×1200 | 1920×1200 | 1920×1200 | 2560×1600 | 4096×2160 | 4096×2160 |

| 60p | 60p | 60p | 75p | 24p | 60p | |

| 最大オーディオ チャネル数 |

8 ch | 8 ch | 8 ch | 8 ch | 8 ch | 32 ch |

これを見てわかるように、HDMI を最大伝送速度で使用するためにはギガ帯域のシリアル転送ができる FPGA を選定します。

つまり、トランシーバ PHY が内蔵されているタイプを選んでください。

下表に、評価ボードを使用して検証済みの FPGA トランシーバ PHY の最大スペックと、Mpression 製 HDMI IP のサポート状況および社内検証で使用した評価ボードを示します。

| Table 2: FPGA トランシーバ PHY の最大スペックおよび HDMI IP のサポート状況と評価ボード | ||||

| デバイス | トランシーバ 最大スペック (bps/ch) |

HDMI | 検証に使用した評価ボード | |

| 1.4b | 2.0a | |||

| 10.2 Gbps | 18 Gbps | |||

| Stratix® V GX/GS | 14.1 G | ○ | ○ | インテル® 製 Stratix® V GX Dev Kit |

| Arria® 10 GX/SX | 17.4 G | ○ | ○ | インテル® 製 Arria® 10 GX Dev Kit |

| Arria® V GX/SX | 6.5536 G | ○ | △ | |

| Cyclone® V GX/SX | 3.125 G | Up to 3.125 Gbps |

- | |

[記号] ○:サポート / △:限定サポート / -:未サポート(未検証)

例えば、HDMI 2.0 の最大帯域幅は 18Gbps(1レーンあたり最大6Gbps)です。

よって最大帯域幅で I/F させるためには、FPGA 内蔵のトランシーバのスペックが 6Gbpsオーバーのものを選定する必要があります。

もしも「今回の帯域は 2.97Gbps までしか使わないぜ!」と言う仕様であれば、Cyclone® V GX (3.125Gbps)も選択肢に入ります。

上表以外のファミリは、社内未検証のため要相談と言うことで。

今回のデモは Cyclone® V GX なので、(HDMI 2.0 のフルスペックには対応していませんが)フレームレートを下げて4K動画を映します。

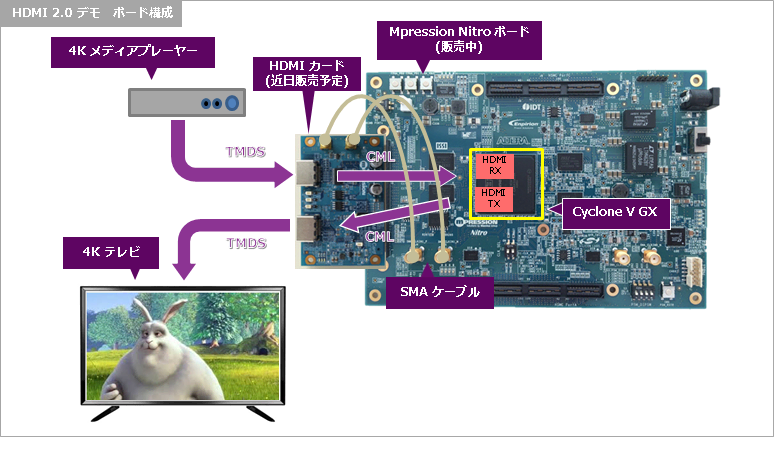

デモの概要

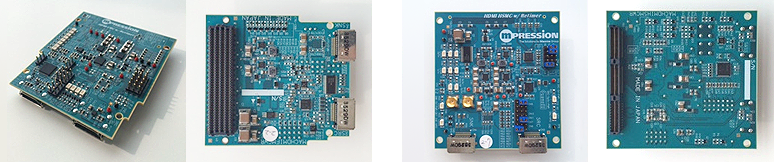

Cyclone® V GX の搭載された Nitro に、これまた Mpression 製の HDMI ドータカード(近日販売予定)を装着して HDMI I/F を検証します。

この HDMI ドータカードは、レベル変換用です。

HDMI のメインリンクは TMDS(Transition Minimized Differential Signaling)方式で、MAX® 10 を除いたインテル® FPGA の I/O では直に接続することができないため、TMDS-CML(PCML)に変換し FPGA へ接続させています。(MAX 10 の TMDS サポートはレシーバのみです。)また、SMA ケーブルは HDMI からのクロックを FPGA へ入力させる目的で、Nitro ボードの専用クロック端子における仕様上このような構成になります。(致し方ありません。)

デモの内容は超シンプル!

メディアプレーヤーで4K動画を再生

⇒ HDMI ケーブルを介して FPGA へ信号を入力

⇒ そのまま FPGA から HDMI ケーブルを介して信号を出力

⇒ 4Kテレビに映像を表示させます。

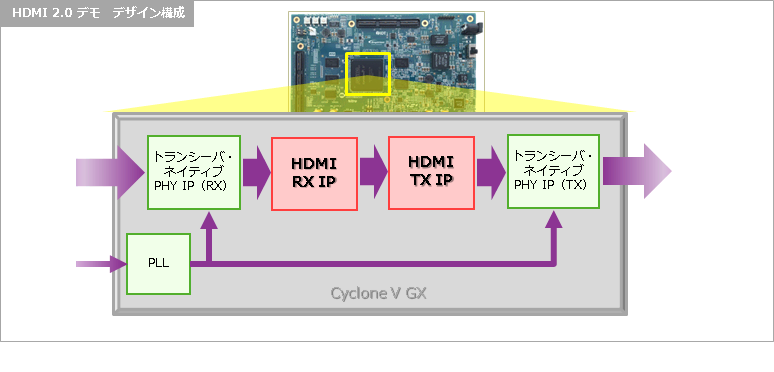

デモ用サンプル・デザイン

FPGA で HDMI I/F させるために最低限必要なデザインは、以下のとおりです。

- トランシーバ・ネイティブ PHY IP(RX/TX)

- Mpression 製 HDMI IP(RX/TX)

- PLL

HDMI IP は、暗号化された VerilogHDL ファイルで提供されます。(Quartus® Prime のコンパイラは言語混在をサポートしているので、VHDL ユーザーも IP をご利用いただけます。)

現在は CD-ROM でお客様へ提供しているそうです。

IP をインスタンスする際の補助ファイル(Quartus® Prime の IP Catalog で言うところの _inst.v/*_inst.vhd、*.cmp)は現在提供していないそうなので、ユーザーズ・マニュアルを見てポート接続部分を記述するか、あるいは HDMI IP と一緒に提供されるサンプル・プロジェクトのデザインを参考にコピペ&編集してインスタンスを接続します。

サンプル・プロジェクトもVerilogHDL での提供なので、VHDL ユーザーさんにはちょっと編集に手間が必要になりますが、開発チームに依頼すればパパっと作ってくれると思いますよ。私からもインスタンス・ファイルを作って欲しいとリクエストを出しておきました♪

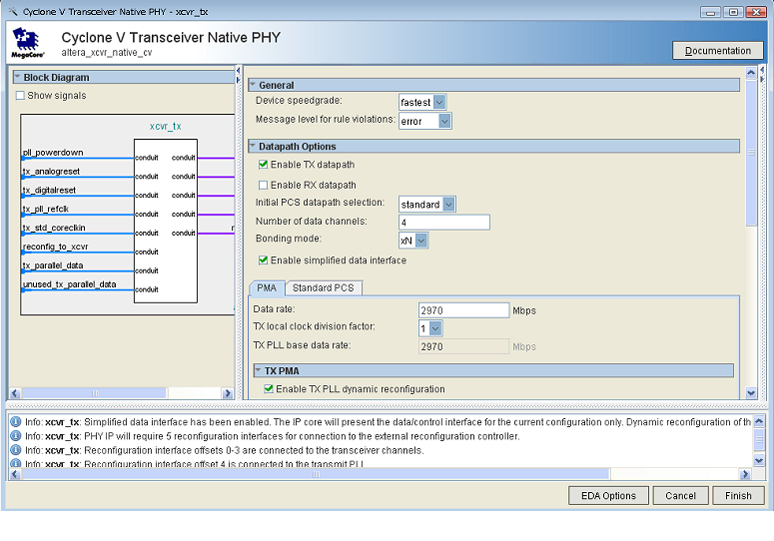

トランシーバ・ネイティブ PHY は、FPGA にハード実装されたトランシーバ部分を構築するために必要な IP マクロで、Quartus® Prime に標準搭載された無償で使用できる IP です。

IP Catalog を使ってターゲット・デバイス向けの Transceiver Native PHY を選択し、ユーザーの仕様に合わせてレシーバ(RX)、トランスミッタ(TX)を個別あるいは共通にライブラリを作ります。希望する帯域幅に合わせてパラメータを設定し完成させます。

仮に FPGA 開発が初めてのユーザーさんでも、サンプル・プロジェクトが提供されるのでそのデザインを参考に作れば簡単にできます。

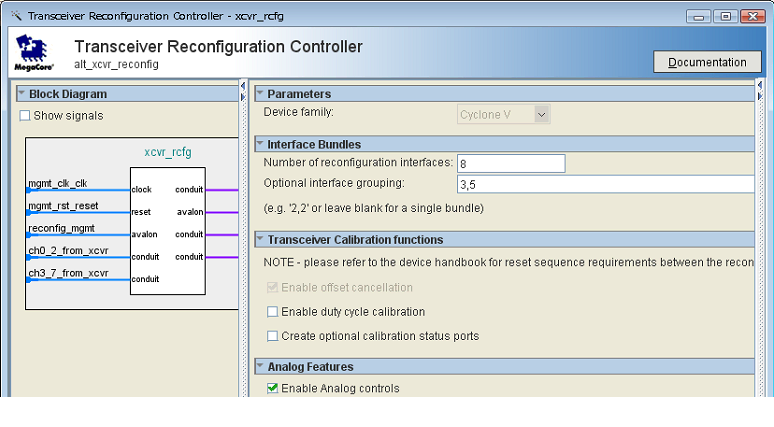

下図は、今回のデモ・デザイン向けに HDMI のデータレート 2.97Gbps 用に構成したトランシーバ(TX)のパラメータ設定画面(一部)です。

PLL は、そのトランシーバ・ネイティブ PHY をドライブするためのクロック周波数の生成用として構成しています。

このマクロも Quartus® Prime に標準搭載されているので無償で使用できます。

こちらも IP Catalog を使って作ります。

こちらもトランシーバ・ネイティブ PHY 同様に、提供されるサンプル・プロジェクトを参考にして自分の仕様に応じた設定値にします。

固定解像度であればこれだけ。

もし解像度を 4K ⇔ フル HD ⇔ HDというように動的に切り替えられるようにする場合には、さらにトランシーバおよび PLL のリコンフィギュレーション用デザイン を作成します。

こちらもトランシーバ・ネイティブ PHY 同様に提供されるサンプル・プロジェクトを参考に、仕様に適用させてください。

下図は、トランシーバ・リコンフィギュレーション・コントローラのパラメータ設定画面(一部)です。

デモ用デザインをシミュレーション

デザイン作成が完成したらファンクション・シミュレーションをします。

Mpression の HDMI IP は、ファンクション・シミュレーション用のライブラリとテストベンチが提供されます。

対応ツールは ModelSim*(Intel® FPGA Edition を含む)のみで、VerilogHDL が用意されています。

もし所有している ModelSim* SE や Questa* が VHDL 限定ライセンスであった場合には言語混在シミュレーションができません。

そんなときは、ModelSim*- Intel® FPGA Edition(Quartus® II 15.0 対応の ver.10.3d 以降)を使用すれば言語混在シミュレーションができますので安心してください。

デモ用デザインをコンパイルおよびタイミング解析

ピン・アサインや各種オプション設定、タイミング制約など、通常の FPGA 開発のフローをたどってください。

タイミング制約用の SDC ファイルは、ユーザーズ・マニュアルに記載された内容を参照して作成します。

その後、コンパイルを実行し、コンパイル・レポートを検証してタイミング解析結果がミートできていることを確認します。

デモ用デザインを実機にプログラミング、そして動画を映してみよう

Quartus® Prime の Programmer でコンフィギュレーション・データをダウンロードします。

その後、テレビの解像度を4Kに設定して、と…。

ほら!きれいに映りました。

ね、IP を使うとこんなに簡単に FPGA で HDMI I/F ができちゃいました。

安心してください。技術サポートも万全です!

Mpression の HDMI IP は、以下のアイテムが用意されています。

- HDMI IP ライブラリ(暗号化 VerilogHDL ファイル)

- HDMI IP シミュレーション・ファイル(ライブラリ、テストベンチ)

- サンプル用 Quartus® Prime プロジェクト一式

- ユーザーズ・マニュアル(もちろん日本語です。)

この他、採用を検討しているユーザーには評価用ラインセンスの発行もしてくれます。

また、IP 開発部隊は日本(新横浜)にいますので技術サポートもクイック・レスポンス!スタッフは日本語で対応します。だから購入後も “安心サポート” なんです。ユーザーのリクエストにも可能な限り対応してくれるみたいですよ。

今回のデモで使用した商品

メインボードとして使用した Mpression 製 Nitro は、こちらで購入できます。

Nitro - Cyclone® V GX I/O拡張ベースボード

Mpression 製 HSMC ドータカードは近日発売予定です。

コネクタはこちらの2タイプを予定しています。(※画像は試作品です。販売品とは若干異なります。)

お問い合わせ窓口

Mpression 製 HDMI 2.0 IP または HDMI ドータカードに興味がある方は、下記へご連絡ください。

以上、インテル・F・ハナコ の体験レポートでした。