概要

FPGA 内に実装されたデザインおよび IP(Intellectual Property)を、複製、リバース・エンジニアリング、および改ざんから保護するためにデザイン・セキュリティ機能を提供しています。

デザイン・セキュリティの仕組み

コンフィギュレーション・データを AES(Advanced Encryption Standard)キーで暗号化することで、コンフィギュレーション・データを傍受されても解読できないようにします。

FPGA の起動は、暗号化されたコンフィギュレーション・データを FPGA 内にある AESキーで復元してから起動します。

このように、暗号化と復号化で同じキーを使う方式を、“共通鍵暗号方式”と言います。

この仕組みでは AESキーが一番重要となりますので、FPGA から AESキーの取り出し/消去/変更はできないようになっています。

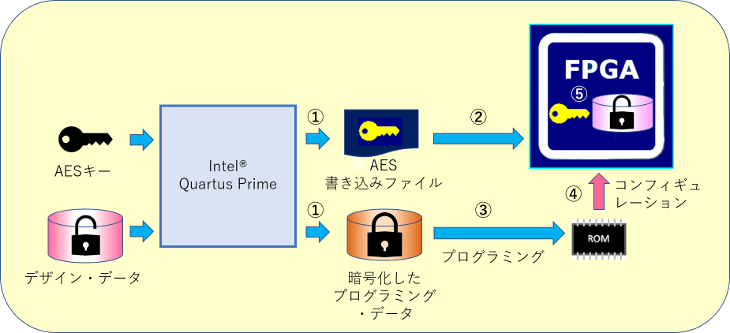

暗号化の作業と起動フロー

1. 書き込みファイルの生成

Quartus® Prime にデザイン・データと任意の AESキーを入力すると、“AES書き込みファイル(.ekp)”と“暗号化されたプログラミング・データ”が生成されます。

2.AESキーを FPGA に書き込み

1.で生成した“AES書き込みファイル”を FPGA に書き込みます。これが、“暗号化したコンフィギュレーション・データ”を復号化するための鍵となります。

3.プログラミング

1.で生成した“暗号化したプログラミング・データ”を外部のコンフィギュレーションROMやフラッシュ・メモリなどに書き込みます。書き込み方法は、通常のプログラミング・データの書き込みと同じです。

4.コンフィギュレーション

AESキーを書き込んだ FPGA を起動すると、外部のROMから“暗号化したコンフィギュレーション・データ”を読み込みます。

5.復元と起動

FPGA 内部にある AESキー(AES書き込みファイル)と復元化回路で、“暗号化されたコンフィギュレーション・データ”を元のコンフィギュレーション・データに自動で復元してから起動します。

AESキーが同じであれば、暗号化した別のプログラミング・データも同じ FPFA で使用できます。

用語説明

用途に応じてデータの名称が変わりますので、混乱を避けるために説明します。

| デザイン・データ | : RTL などの回路設計データ |

| プログラミング・データ | : コンフィギュレーション用ROM に書き込むためのデータ |

| コンフィギュレーション・データ | : FPGA に書き込むためのデータ |

2種類の AESキー

AESキーには揮発性と不揮発性の2種類のキーがあります。

どちらも、複製・リバースエンジニアリング・不正改ざんを強力に防止します。

FPGA で扱えるAESキー

FPGA は揮発性 または不揮発性のAESキーを使用できます。

・揮発性キー

揮発性キーは、FPGA に内蔵している揮発性(電源が無いとデータが消える)の SRAMメモリ に AESキーを保存します。

AESキーの変更や消去は可能ですが、常に外部電源でデータをバックアップしておかないと AESキーが消滅します。

揮発性AESキーは、試作時のコンフィギュレーション・データを保護するのに便利です。

・不揮発性キー

不揮発性キーは、FPGA に内蔵されたヒューズを使った不揮発性キーに AESキーを保存します。

AESキーの書き込みはヒューズを物理的に切断するので、外部電源のバックアップは不要で、一度書き込むと AESキーの変更や消去はできません。

メーカーであっても FPGA の不具合解析はできなくなり、JTAG は 1149.1/1149.6 (JTAG Boundary scan test )以外の命令を受け付けなくなります。

不揮発性キーは、安全性が高く、“量産時のコンフィギュレーション・データ”を保護するのに役立ちます。

| キーの種類 | キー長 | 変更や消去 | 外部電源 | キー書き込み方法 | お勧め |

| 揮発性キー | 256bit | 可能 | 必要 | オン・ボード | 試作 |

| 不揮発性キー | 256bit | 不可能 | 不要 | オン・ボード/オフ・ボード | 量産 |

CPLD (MAX® 10) で使えるAESキー

MAX® 10 に内蔵している不揮発性のフラッシュROMに AESキーを保存できます。フラッシュROMなので、変更や消去が可能で、データを保存するための外部電源も不要です。

MAX® 10 は ヒューズを使った不揮発性キーは内蔵していません。

| キーの種類 | キー長 | 変更や消去 | 外部電源 | キー書き込み方法 | お勧め |

| 不揮発性キー | 128bit | 可能 | 不要 | オン・ボード/オフ・ボード | 試作&量産 |

AESキーの書き込み方法

AESキーの書き込みには、オン・ボードとオフ・ボードによる書き込み方法があります。

オン・ボード

オン・ボードは、基板に実装済の FPGA デバイスにケーブルなどを介して AESキーを書き込む方法です。

基板上にケーブルを接続する端子が必要ですが、ご自身で書き込むことができます。

オフ・ボード

オフ・ボードは、実装前の FPGA に直に AESキーを書き込む込む方法です。

専用のプログラマーを使うので、書き込みの信頼度が高く、書き込み速度が早いのが特徴です。

ただし、書き込み用のプログラマーと FPGAを接続するためのソケット(アダプタ)が必要なので費用が掛かります。

マクニカのプログラミング・センターは AESキーを書き込めるプログラマーを複数台保有しており、書き込み実績が豊富です。

マクニカにてAESキー書き込みをご希望の方はお気軽にお問い合わせください。

| 書き込み方法 | 書き込みツール | 最適な書き込み数量 |

| オン・ボード | JTAG/Ethernet Blaster/USB- Blasterなど | 少数~中量 |

| オフ・ボード | 書き込み専用のプログラマー | 中量~大量 |

MAX® 10 の場合は、AESキーと暗号化したコンフィギュレーション・データを一緒、または別々にデバイスに書き込むことができます。

オン・ボード、オフ・ボードでも、暗号化していない通常のコンフィギュレーションと同じオペレーションで MAX® 10 に AESキーを書き込めます。

不揮発性キーを FPGA の外に置く方法

FPGA にワンタイムの不揮発性キーを書き込むのが心配な方には、FPGA の外に不揮発性の AESキーを 置く方法があります。

デザイン・ゲートウェイ社の 「IP Lock」は、基板上に AES専用の“暗号処理チップ”を実装し、FPGA 内の“復元回路”でコンフィギュレーション・データを復号化するソリューションです。

この“暗号処理チップ”は変更や消去ができないワンタイムのキーですが、“小さく”て“安価”なのが特徴です。

AESキーの書き込みに失敗したり、キーを変更するには、“安価”な暗号処理チップを取り換えればいいので、FPGA を取り換えるよりもリスクを小さくできます。 ハイエンドで高価な FPGA の暗号化には「IP Lock」をお勧めします。

<基板に実装した暗号処理チップ(赤丸部分)>

<IP Lockライター>

IP Lock のメリット

・128bitの AESキー+32bitのプロダクトID で保護!

・プロダクトIDとして、暗号処理チップと IP Lockライター も認証!

・1秒間に約5回の周期で認証データを変更・暗号化!

・小さく安価な専用の暗号処理チップ!

・量産用に安価で信頼性の高い専用の書き込み機「IP Lockライター」をご用意!

・FPGA の種類毎に、大きな ソケット(アダプター)を購入する必要なし!

・信頼ある国内業者の製品。日本語による手厚いサポート有!

IP Lock の制約

IP Lock は AESキーを FPGA 外部に配置するので、若干制約があります。

・暗号処理チップの AESキー書き込みは1回のみ、変更や書き込みに失敗すると暗号処理チップの取り換えが必要

・暗号処理チップに AESキーの書き込み作業が必要(請負可能)

・基板上にあらかじめ 暗号処理チップ(SOIC-8)を配置する領域と配線(2本)が必要

・ユーザーロジックに AES復元回路(1.3K LE + 25K bit mem)が必要

ラボラトリーズパック

お試し用に、あらかじめ AESキーを埋め込んだ暗号処理チップを10個、AESキー毎の復元回路、日本語マニュアルをパッケージにした「ラバトリーパック」をご用意しています。

AESキーと復元回路は対になっており、各パック毎にAESキーは異なります。