FPGAなど多くの半導体デバイスは、複数の電源を必要とします。その際に、電源シーケンスを守ることを要求されるため、電源のオン・オフ制御ピンや出力コンデンサーのディスチャージ機能が必要となる場合があります。

今回は、LDOを使用した場合の注意点4つに絞って、説明致します。

シーケンスを組むためにオン・オフ機能が必須

最近のFPGAやDSPは、電源のオン・オフシーケンスを要求することが一般的です。オン・オフを制御するためには、電源IC(モジュール)にオン・オフ制御用のイネーブルピンが必要になります。安価なLDOには、オン・オフ制御用のピンが無い場合があるので選定には注意が必要です。

立ち上がり時間の制御

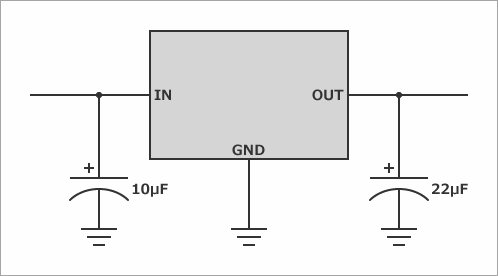

ソフトスタート機能があれば、立ち上がり時間の制御をおこなうことができます。しかし、LDOでソフトスタートの機能を持っている製品は少ないです。対策としては、出力のコンデンサーの容量で立ち上がり時間を制御する必要がでてきます。ただし、あまり大きなコンデンサーを付けてしまうと立ち下げ時に問題を引き起こしてしまいます。

電源の立ち下げシーケンス

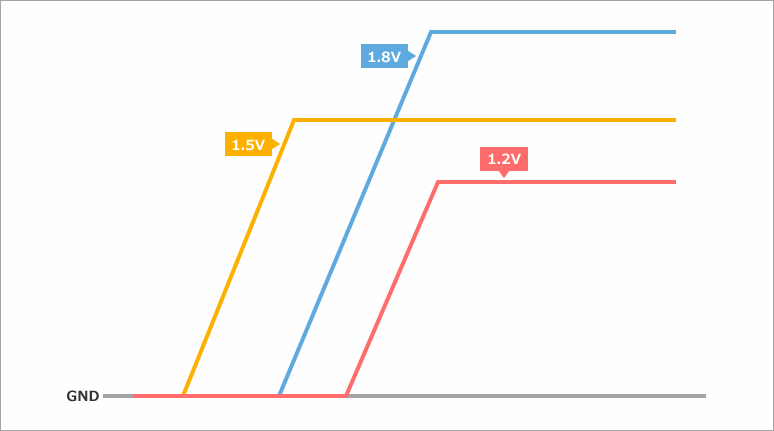

立ち上げシーケンスの規定は、よく知られています。しかし、立ち下げシーケンスに関してはあまり今まで注意されていませんでした。最近は、基板上に搭載される電源数も多く、立ち下り時のシーケンスも十分注意しないとラッシュカレントを流してしまうケースがあるため、立ち下げシーケンスも十分注意することが重要です。

シーケンスが必要な理由は、こちらの記事を参考にしてください。

電源シーケンスは必要ない?

立ち上がりシーケンスのため、LDOの出力コンデンサーを大きくして調整すると、立ち上げ時間を長くする観点では良いのですが、立ち下げの時間が長くなるため(コンデンサーの放電時間が長くなる)、立ち下げシーケンスに対して不利になるので注意が必要です。

LDOの立ち下げシーケンス

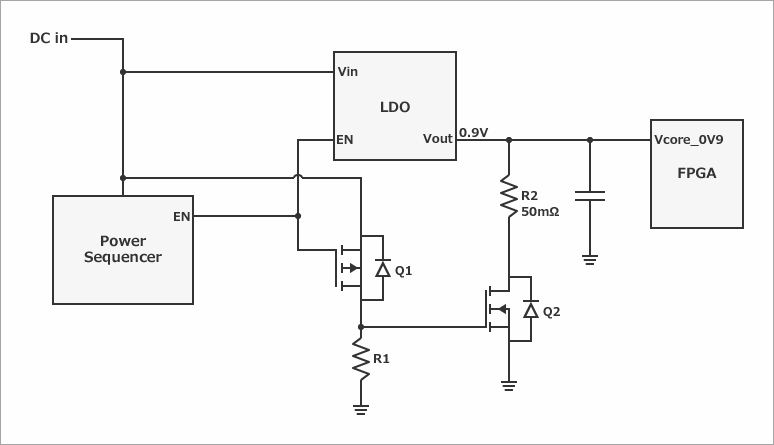

スイッチングレギュレーターは、Low SideのFETがOff時にディスチャージしてくれる場合、出力電圧が直ぐに落ちてくれるので、オフシーケンスも簡単に組めることもあります。しかし、LDOの出力側のディスチャージ機能は無いものがほとんどです。

そのため、出力コンデンサーを大きくすることによる、立ち上げシーケンス制御はお勧めできません。仮に必須になった際は、外付けにディスチャージ用の回路を追加する必要があります。

オン・オフ機能とディスチャージ機能を持ったLDO

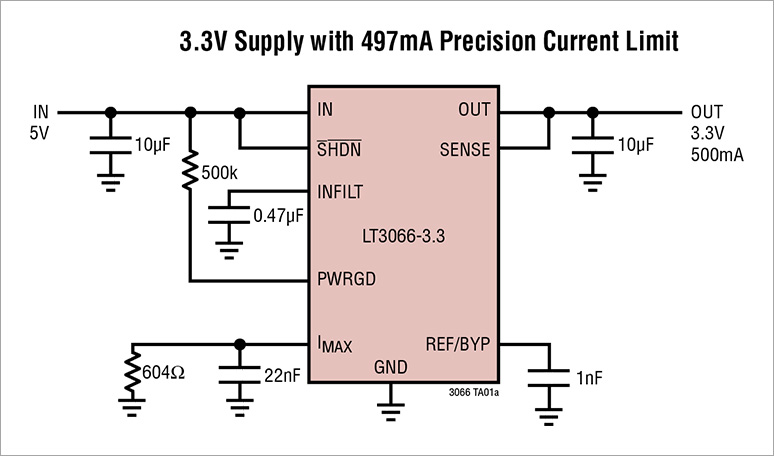

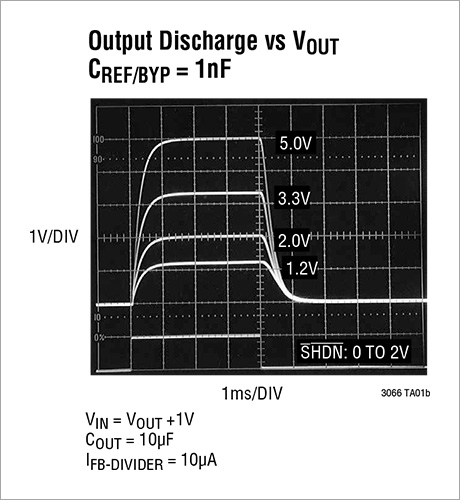

アナログ・デバイセズ社のLDOには、オン・オフ機能(図4のSHDN PIN)や出力部の電荷をディスチャージする機能を持った、LT3066と言うようなLDO製品があります。

図5が出力のディスチャージ機能により、出力電圧を早く0Vしている波形になります。

このような機能があることで、FPGAが要求するパワーダウン・シーケンスをおこないながら、LDO製品によりPLLやアナログ電源に対してクリーンな電圧供給するをおこなうことが可能になります。

商品の購入はこちら

お問い合わせ

本記事に関してご質問などありましたら、以下よりお問い合わせください。

アナログ・デバイセズ メーカー情報 Top へ

アナログ・デバイセズ メーカー情報 Top ページへ戻りたい方は、以下をクリックください。