はじめに (INTRODUCTION)

本記事では、統合導体を備えた電流センサーの放熱を改善するために、インパッドビアおよびその他の追加のプリント基板 (PCB) レイアウト技術を使用することの有効性について説明します。IC がその最大接合部温度である 165℃ を超えるのを防ぐためには、最適なヒートシンクが必要です。

背景 (BACKGROUND)

統合されたアレグロ電流センサーパッケージ

アレグロの電流センサー ICファミリーは、完全に統合された電流検出ソリューションであり、電力密度において業界をリードしています。電流は統合された導体リード (IP+、IP-) を通ってパッケージに入り、その導体の抵抗が熱を発生させます。この熱は、IC の温度を 165℃ 未満に維持するために放散させる必要があります。アクティブなヒートシンクがない場合、パッシブなヒートシンクの主な源は PCB 自体への放熱です。統合導体に直接接続される金属が多いほど、ヒートシンクはより効果的になります。本記事の目的は、PCB へのパッシブヒートシンクを最大化する方法を説明することです。

本記事に含まれる統合電流センサーパッケージの概要は、表1 に記載されています。さまざまなアレグロ電流センサーパッケージに適用された検出電流に対する、25℃ からのダイの加熱の比較を図1 と図3 に示します。また、125℃ からのダイの加熱と適用された検出電流の比較を図2 と図4 に示します。

図1:インパッドビア — 高沿面パッケージに関するアレグロのラボ結果、25℃ ※Allegro MicroSystems 社より提供

図2:インパッドビア — 高沿面パッケージに関するアレグロのラボ結果、125℃ ※Allegro MicroSystems 社より提供

図3:インパッドビア — 低沿面パッケージに関するアレグロのラボ結果、25℃ ※Allegro MicroSystems 社より提供

図4:インパッドビア — 高沿面パッケージに関するアレグロのラボ結果、125℃ ※Allegro MicroSystems 社より提供

表1:アレグロ集積型電流センサーパッケージの概要※Allegro MicroSystems 社より提供

[1] PCB レイアウトに関する推奨事項は、付録に記載されています。

[2] 認証は現在申請中です。

[3] RθJA は、パッケージ内で消費される電力によって発生した熱が、チップ上の回路(ジャンクション)から周囲環境へ伝わる際のシステムレベルの熱抵抗を示します。RθJA は一般に、JESD51 で規定された 2 層 PCB レイアウトを基準として定義されます。しかし電流センサーの場合、JEDEC 標準基板は高電流に対応できないため適切ではありません。本資料で定義されている RθJA は、本記事で言及している 高電流の伝送に最適化されたアレグロの評価基板を基にしています。RθJA は PCB や使用環境に大きく依存しますが、パッケージの熱性能を概算で評価するため、またパッケージ間の比較を行う指標として有用です。

[4] ΨJT は、パッケージ内で消費される電力に対する熱指標であり、ジャンクション温度とパッケージ上面の最高温度との差として定義されます。この指標は、パッケージ上面の温度を測定することでジャンクション温度を推定するための、簡便な手法として有用です。この値は PCB や使用環境に大きく依存します。技術的には「熱抵抗」ではなく、負の値を取る場合もあります。これは、ほとんどの IC パッケージとは異なり、主な発熱源(内蔵電流ループ)がダイと同じ位置に存在しないためであり、パッケージ上面の温度がジャンクション温度よりも高くなる場合に、負の値となることがあります。

インパッドビアの利点 (BENEFITS OF IN-PAD VIAS)

インパッドビア技術は、表面実装部品のパッド直下にビアを配置し、内層と最上層を接続するものです。インパッドビアを使用する場合、はんだが穴に吸い込まれてはんだ接合の品質が低下するのを防ぐために、ビアを充填する必要があります。最も一般的なビア充填材は非導電性です。ビアは電気的および熱的に導電性のある材料で充填することもできますが、これは非導電性材料よりも高価になる傾向があり、非導電性充填材に比べてわずかな改善しか得られません。LZ パッケージの銅パッド下にビアがある場合とない場合の比較を図5と図6に示します。

図5:LZ パッケージを例とした、銅パッド下のビア

※Allegro MicroSystems 社より提供

図6:LZ パッケージを例とした、銅パッド下にビアがない場合

※Allegro MicroSystems 社より提供

インパッドビアは、一般的に熱性能、省スペース、および電気抵抗の低減のために使用されます。

- 熱性能:図5 に示すように、ビアを統合導体リードの直下に配置することにより、PCB パッドは電流導体と放熱の両方の役割を果たします。この方法により、部品で発生した熱は基板を通って内側の金属層へより効率的に放散され、そこで熱は部品からより効率的に拡散されます。

- 省スペース:パッド直下にビアを配置することは、スペースが限られている一部の設計で役立ち、部品をより近接して配置できます。ただし、ビアを放熱に使用する場合、熱伝導のための中断のない金属プレーンの量を最大化するために、統合導体の近くの追加部品は最小限に抑える必要があります。

- PCB トレース抵抗の低減:ビアが PCB 内の複数の層を直接並列に接続するため、電流源から統合導体リードまでの PCB 上の抵抗を最小限に抑えることができます(図5 参照)。IC 周辺の通電層の抵抗は PCB 内で熱を発生させ(図9 参照)、IC 周辺の PCB 温度を上昇させます。これにより、熱が IC から離れて流れるための温度勾配が減少し、放熱効率が低下します。

インパッドビアと非インパッドビアの結果比較 (RESULTS OF IN-PAD VIAS VERSUS NO IN-PAD VIAS)

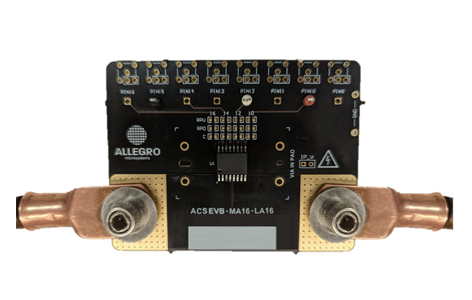

Allegro MicroSystems は、ラボ環境でアレグロの電流センサーを迅速に評価するために、最適化されたヒートシンクを備えた評価ボードを提供しています(図9 参照)。以下の比較では、これら 2つの評価ボードからデータを収集しています。ボードは、一方がインパッドビアを持ち、もう一方がパッド外にビアを持つ点を除いて同一です。(LC/LZ パッケージの評価に使用された 2つの評価ボードを図7 と図8 に示します。他のすべてのパッケージについては、インパッドビアを示す参照レイアウト図が付録に記載されています。これらの図は縮尺通りではないことに注意してください)。インパッドビアで使用される各ビアのサイズは 0.5mm です。ビアの種類は IPC-4761 タイプVII:充填およびキャップ付きビアです。非導電性のビア充填材が使用されています。これらのボードは 6層で、各層は 2オンスの銅箔です。

図7:インパッドビアありの LC/LZ PCB レイアウト参照図

※Allegro MicroSystems 社より提供

図8:インパッドビアなしの LC/LZ PCB レイアウト参照図

※Allegro MicroSystems 社より提供

テストは 25℃と 125℃ の周囲温度で実施されました。電流は 2AWGゲージのケーブルを介して PCB に供給されました。その後、DC電流がデバイスの統合導体リードに流されました。ダイの温度は、熱平衡に達した後にオンチップの温度センサーを使用して測定されました。(このオンチップ温度センサーは顧客には利用できません)。ダイ温度の変化は、測定されたダイ温度から測定された周囲温度を差し引くことによって決定されました。

すべてのパッケージについて、インパッドビアの有無による熱性能の比較は、以下のプロットで確認できます。さらに、25℃ と 125℃ での熱性能の比較もプロットで確認できます。

注:125℃ でのテストには、インパッドビアを備えた評価ボードのみが使用されました。前述のように、ダイの温度は 165℃、または室温からの上昇分 140℃ (140°C + 25℃= 165℃) を超えてはなりません。

データは、インパッドビアを使用しない場合と比較して、インパッドビアを使用する方がダイの温度上昇が小さいことを示しています。統合導体を備えたすべての電流センサーに対して、アレグロはインパッドビアの使用を推奨します。

最も正確な結果を得るために、アレグロは手はんだ付けではなく、標準的なリフロープロセスで部品を実装することを推奨します。はんだが多すぎたり少なすぎたりすると、結果に影響を与える可能性があります。これは特に QFNタイプのパッケージ(EZおよびEX)に当てはまり、部品の下のはんだボイドが見えず、PCB へのヒートシンクに大きな影響を与える可能性があります。

■ LZ パッケージ

図10:インパッドビア有無による LZ パッケージの比較

※Allegro MicroSystems 社より提供

図11:インパッドビアを有する LZ パッケージの比較(周囲温度 25℃ / 125℃)

※Allegro MicroSystems 社より提供

■ LC パッケージ

図12:インパッドビア有無による LC パッケージの比較

※Allegro MicroSystems 社より提供

図13:インパッドビアあり LC パッケージの比較(周囲温度 25℃ / 125℃)

※Allegro MicroSystems 社より提供

■ MA パッケージ

図14:インパッドビア有無による MA パッケージの比較

※Allegro MicroSystems 社より提供

図15:インパッドビアあり MA パッケージの比較(周囲温度 25℃ / 125℃)

※Allegro MicroSystems 社より提供

■ LA パッケージ

図16:インパッドビア有無による LA パッケージの比較

※Allegro MicroSystems 社より提供

図17:インパッドビアあり LA パッケージの比較(周囲温度 25℃ / 125℃)

※Allegro MicroSystems 社より提供

■ MC パッケージ

図18:インパッドビア有無による MC パッケージの比較

※Allegro MicroSystems 社より提供

図19:インパッドビアあり MC パッケージの比較(周囲温度 25℃ / 125℃)

※Allegro MicroSystems 社より提供

■ EZ パッケージ

図20:インパッドビア有無による EZ パッケージの比較

※Allegro MicroSystems 社より提供

図21:インパッドビアあり EZ パッケージの比較(周囲温度 25℃ / 125℃)

※Allegro MicroSystems 社より提供

■ EX パッケージ

図22:インパッドビア有無による EX パッケージの比較

※Allegro MicroSystems 社より提供

図23:インパッドビアあり EX パッケージの比較(周囲温度 25℃ / 125℃)

※Allegro MicroSystems 社より提供

■ LH パッケージ

図24:インパッドビア有無による LH パッケージの比較

※Allegro MicroSystems 社より提供

図25:インパッドビアあり LH パッケージの比較(周囲温度 25℃ / 125℃)

※Allegro MicroSystems 社より提供

■ MY / MZ パッケージ

図26:インパッドビアあり MY / MZ パッケージの比較(周囲温度 25℃ / 125℃)

※Allegro MicroSystems 社より提供

銅の温度係数の影響 (Impact of the Temperature Coefficient of Cu)

内部導体は、主に銅と少量の他の金属で構成される銅合金であり、その熱挙動は純銅と同様と見なすことができます。銅は正の抵抗温度係数(1℃ あたり +0.393%)を持っており、これは導体の温度が上昇するにつれてその抵抗も増加することを意味します。これは、電流が流れていない状態で周囲温度が 100℃ 上昇すると、パッケージで消費される電力がほぼ 40% 増加することに相当します。

例えば、MA パッケージに 50Arms の電流を流した場合、25℃ の周囲温度で 0.85mΩ の抵抗を持つと、パッケージ内で 2.125W の電力を発生させます。125℃ の周囲温度では、発生する電力は2.95W に増加します。これには、電流が流れるときに導体で消費される電力による温度上昇は考慮されていません。この正のフィードバックは、熱暴走の可能性を減らすために、パッケージから効率的に熱を除去するさらなる理由となります。

追加の基板レイアウトに関する考慮事項 (Additional Board Layout Considerations)

これらの評価ボードを設計する際には、考慮すべき追加の重要な事項があります。

- パッドレイアウト:最適な熱性能を得るために、最上層の銅層を一次電流パッドと完全に重ね合わせ、IP+ と IP- の内部導体ピンを隔てる小さなギャップのみを残すことが推奨されます。重なり合う領域のビアのサイズと数量は、PCB 製造プロセスの設計ルールに基づいて最大化する必要があります。

- 熱管理:接合部温度を 165℃ 未満に保つためには、システムレベルで追加のパッシブヒートシンクやアクティブ冷却技術が必要になる場合があります。絶縁されたアプリケーションでは、パッケージのクリーページ距離を損なう可能性があるため、パッケージの上部にヒートシンクを追加することはお勧めできません(ただし、適切な高電圧絶縁方法に従う場合を除く)。ほとんどの誘電絶縁材料は優れた断熱材でもあるため、パッケージとヒートシンクの間に絶縁を追加すると、一般的にヒートシンク効果が減少します。パッケージの上部を通るパッシブヒートシンクは問題が多く、PCB を介した放熱が好ましい方法です。

- 部品配置:電流センサーの近くに大量の熱を発生させる他の部品があると、電流センサーから熱が流れ出るための温度勾配が減少する可能性があります。最良の設計方法は、熱を発生させる部品をできるだけ離して配置することです。

- 銅層:厚い銅層には 2つの利点があります。部品からの熱伝導が向上し、熱を発生させる電気抵抗が低くなります。各層の厚さを最大化し、インパッドビアを介して電流センサーと直接接触する層の数を最大化することで、ダイの接合部温度を最小限に抑えます。

- トレース幅:大電流トレースは、電圧降下とインダクタンスを最小限に抑え、過度の発熱を防ぐのに十分な幅が必要です。電流センサーの周りには、実用的な最大の PCB トレースと基板面積を使用することが推奨されます。

- はんだステンシル:QFN EZ パッケージの大きな電流導体パッド(IP+ から IP-)上のはんだのボイドは、はんだ接合の抵抗を増加させ、PCB へのヒートシンクを減少させます。はんだ接合のボイドは最小限に抑える必要があります。ボイドは、はんだフラックスのガス放出によって生じることがあります。はんだリフロー中にはんだの下からガスが逃げる経路を提供することで、ボイドを最小限に抑えることができます。はんだステンシルにグリッドを追加すると、リフローのはんだ濡れプロセス中にパッケージの下からガスが逃げる経路が作成されます。

結論 (CONCLUSION)

アレグロの電流センサーの銅パッドの下にビアを配置すると、パッドの外側にビアを配置する場合と比較して、電流経路の抵抗が最小限に抑えられ、PCB へのヒートシンクが改善され、最適な熱性能が得られます。統合導体電流センサーの動作中のダイの加熱をさらに最小限に抑えるために、追加の標準的なレイアウト技術を実装することができます。

付録 (APPENDIX)

■ PCB レイアウト参照 (PCB Layout References)

図27:EX PCB レイアウト参照図

※Allegro MicroSystems 社より提供

図28:LC PCB レイアウト参照図

※Allegro MicroSystems 社より提供

図29:MA / LA PCB レイアウト参照図

※Allegro MicroSystems 社より提供

図30:MY / MZ PCB レイアウト参照図

※Allegro MicroSystems 社より提供

図31:MC PCB レイアウト参照図

※Allegro MicroSystems 社より提供

図32:LZ PCB レイアウト参照図

※Allegro MicroSystems 社より提供

図33:EZ PCB レイアウト参照図

※Allegro MicroSystems 社より提供

■ インパッドビアのレイアウト参照を示す最上層 (Top Layer Showing Layout References of In-Pad Vias)

図34:EX PCB レイアウト参照図

※Allegro MicroSystems 社より提供

図35:LC PCB 最上層

※Allegro MicroSystems 社より提供

図36:MA / LA PCB 最上層

※Allegro MicroSystems 社より提供

図37:MC PCB 最上層

※Allegro MicroSystems 社より提供

図38:EZ PCB 最上層

※Allegro MicroSystems 社より提供

図39:LH PCB 最上層

※Allegro MicroSystems 社より提供

図40:MZ / MY PCB レイアウト参照図

※Allegro MicroSystems 社より提供

改訂履歴 (Revision History)

| 番号 | 日付 | 内容 | 責任者 |

| - | 2023年8月28日 | 初版リリース | K. Hampton |

| 1 | 2023年10月2日 | 表1(2ページ)に熱特性値を追加。表1(2ページ)に脚注とを追加。ワイヤゲージサイズを修正(3ページ)。軽微な編集上の更新(全ページ)。 | K. Hampton |

| 2 | 2024年1月24日 | 125°Cのアプリケーション情報を追加(2ページ)、軽微な編集上の更新(全ページ)。 | K. Hampton |

| 3 | 2024年2月13日 | 図1 のキャプションの温度を修正(1ページ)。 | K. Hampton |

| 4 | 2024年9月23日 | LH パッケージを追加(全ページ)。未来形(will)の削除、用語の標準化(vias-in-padをin-pad vias に統一)など、全体にわたって軽微な編集上の変更を実施。 | K. Hampton |

| 5 | 2025年1月9日 | MY および MZ パッケージを追加(全ページ)。図1 と図2 を更新(1、2ページ)。熱抵抗メトリクスの丸め計算を更新(4ページ)。関連ドキュメントおよびアプリケーションサポートページを削除(13ページ)。 | K. Hampton |

著作権および免責事項 (Copyright and Disclaimer)

Copyright 2025, Allegro MicroSystems.

この文書に含まれる情報は、この文書の主題に関してお客様に対するアレグロからのいかなる表明、保証、確約、または勧誘をも構成するものではありません。提供される情報は、この情報に基づくプロセスが信頼できること、またはアレグロがすべての考えられる故障モードを調査したことを保証するものではありません。最終製品が信頼でき、すべての設計要件を満たしていることを確認するために十分な認定試験を実施することは、お客様の責任です。

この文書のコピーは、管理されていない文書と見なされます。

お問い合わせ

本記事に関して、ご質問などありましたら以下よりお問い合わせください。

Allegro MicroSystemsメーカー情報Topページへ

Allegro MicroSystemsメーカー情報Topページへ戻りたい方は、以下をクリックください。