Hello. I'm Hanako Altera, who provides technical support for Altera® FPGA products at Macnica.

その1~その3と進んできて、FPGA を開発するための環境が整ったこところで、早速実践です。作業の進め方(フロー)をここで説明します。

Flow of FPGA development

There are roughly eight steps in FPGA development (steps 2 to 9 in the diagram below). Steps 3 and 5 to 9 are done with Quartus® Prime, and step 4 is done with an EDA simulator such as Questa* - Intel® FPGA Edition.

Please refer to the Altera® FPGA development flow page for the operation manuals of the tools for each process.

1. Preparation

FPGA 開発ソフトウェア Quartus® Prime を使用するためのパソコン環境の整備や、開発ソフトウェアのセットアップなど、準備をします。

詳細は以下のページを参考にしてください。

開発に必要なパソコン環境について

開発ソフトウェアのセットアップについて

2. Examination of functional specifications

Based on the system specifications, consider the functions to be implemented in the FPGA (how to process them), and summarize them in specifications such as block diagrams, external interfaces, and inter-block interfaces.

Also, select a family of FPGAs that meets the specifications.

If you plan to use the internal functions inherent in the FPGA, such as PLL (Phase Locked Loop), multiplier block, RAM block, etc., use the FPGA development software Quartus® Prime in advance. Or, use a simulator such as Questa* - Intel® FPGA Edition to create a simple sample design and perform logic verification (RTL simulation) to check operation.

3. Logic circuit design

The operation of logic circuits is described using HDLs (hardware description languages) such as VHDL, Verilog-HDL, and SystemVerilog. Design can also be done using dedicated schematic editors, but in recent years design using languages has become mainstream. These descriptions are mainly called "designs".

Although HDL can be written using a general-purpose text editor, the text editor built into Quartus® Prime is recommended because it has features not available in general-purpose text editors, such as the ability to insert templates and sample designs, and the convenient function of displaying characters in color according to grammar.

In addition, the size and speed of HDL circuits vary depending on how they are written, just like C programs. Quartus® Prime automatically optimizes user-created designs according to the architecture (structure) of the target device.

To use functional blocks (such as multipliers, memory, PLLs, transceivers, etc.) installed in FPGAs, use the Quartus® Prime IP Catalog tool. Select a dedicated block that is already available in the IP Catalog, and customize it by selecting and changing the port configuration and parameters. After that, generate a file and connect it to your design and incorporate it. (IP: Altera® FPGA Intellectual Property)

For information about Altera® FPGA Intellectual Property, please see below.

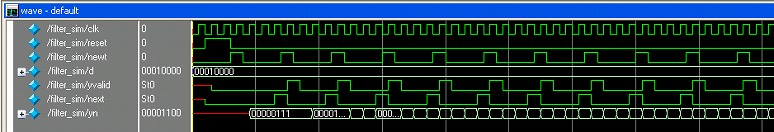

4. Logical simulation

A simulator such as Questa* - Intel® FPGA Edition is used to check (verify) the logic operation on a personal computer to see if the operation of the designed logic circuit (design) meets the user's requirements.

The method of checking the simulation execution results is mainly to use graphically displayed waveforms. If there are operating points that differ from the specifications, it means that the description of the designed logic circuit is incorrect, so correct the description. , and check the behavior again in simulation. Repeat this process to complete the description of the logic circuit.

At this time, input signal data (also called test pattern or test bench) to the verification target circuit is required in addition to the design of the logic circuit realized by FPGA. The testbench allows the user to write test pattern information according to specifications in HDL language and load it into the simulator.

Since the testbench is written by the user, if this input pattern is different from the specification, the verification itself will be a waste of work.

If you are new to HDL design, please refer to sample sources such as reference books when writing.

テストベンチの記述に関しては、以下の記事も是非ご覧ください。

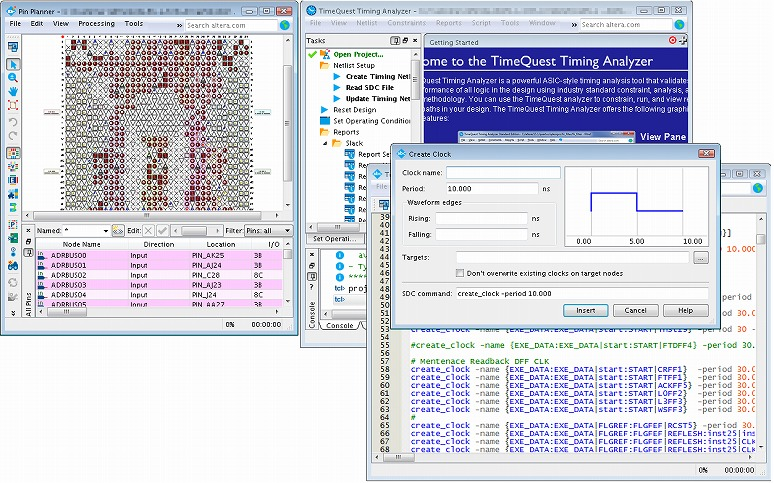

5. Constraint setting

In FPGA development, the user does the pin layout of the device themselves.

Depending on the placement environment of the FPGA and peripheral devices on the board, determine the location of the pins on the FPGA side so that the wiring is short.

Also, FPGA pins have various built-in functions, such as the ability to change the output pin drive current, internal pull-up resistors, and the ability to enable internal termination resistors. Applying the pin function to the device is accomplished by setting options and compiling in Quartus® Prime.

In addition, the operating speed of the FPGA is also set by the user as a timing constraint. Unlike ASSPs, which have fixed operating frequencies, FPGAs rely on the configuration of user-created logic circuits. Of course, there is a limit to the speed of FPGAs, so at the stage of considering adoption, it is necessary to select a family that has specifications such as the clock frequency to be introduced and the data transfer speed with peripheral devices that can be achieved, but the desired timing By setting conditions, the Quartus® Prime Compiler will realize the optimal gate configuration and placement.

These constraints need to be set and input in Quartus® Prime before compilation (logic synthesis and place-and-route). Graphical tools such as Pin Planner: left) and Timing Analyzer (timing analyzer: right) are used. Timing constraints are in the SDC format, which is standard in ASIC design. A wizard for creating the SDC code is also provided as an auxiliary function, so users who do not know the SDC format can easily describe timing constraints.

6. Compile

After creating the design and setting various constraints, execute “Compile”.

Compilation is a general term for work that mainly performs "logical synthesis" and "placement and routing". Quartus® Prime initiates these tasks by simply clicking an icon on the screen, and then automatically performs them.

“Logic synthesis” is the work of converting a design created by the user in an HDL description language or a schematic into concrete gate circuits such as ANDs and flip-flops, which conforms to the structure of the FPGA used by Quartus® Prime. Automatically converts with the optimal gate configuration.

After that, according to the structure of the FPGA to be used, internal logic placement and pin positions are determined as specified by the user, and routing is automatically performed between logic and between logic and pins. This is called “place and route”.

When the compilation is finished, the results of various compilation processes are generated as a report, and the contents can of course be checked using the GUI.

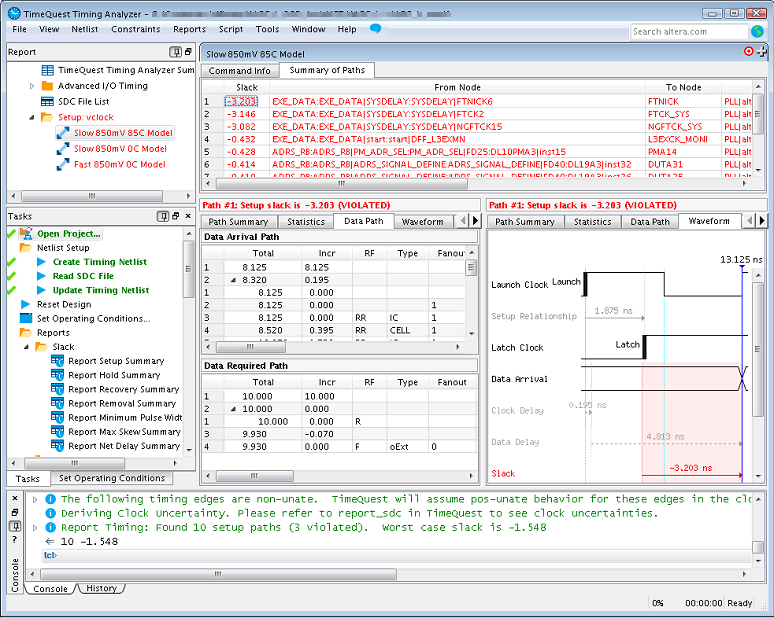

7. Timing Verification

The compilation report also contains timing analysis results.

The user must confirm whether the circuit implemented in the device operates at the required speed (whether the required values set by the timing constraints are met). Timing analysis results in the compilation report are only summary information, so to see detailed results, use the Timing Analyzer in Quartus® Prime and verify statically.

If the results do not satisfy the required values, use the Quartus® Prime options to change the placement and routing algorithm, apply the device functions, and recompile to change the internal layout. We will try to improve by doing so.

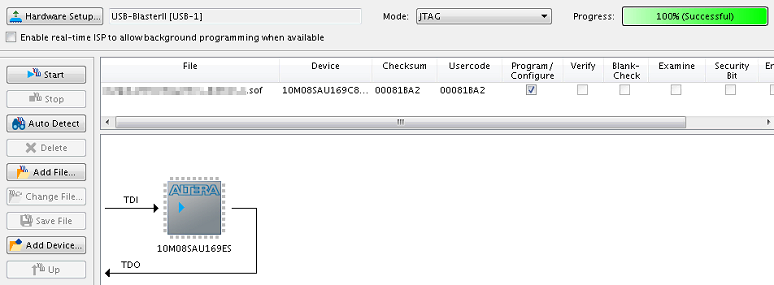

8. プログラミングする

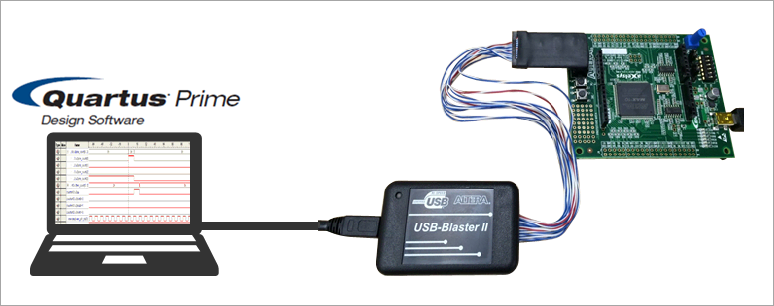

After the timing analysis shows that the circuit works correctly as requested by the user, the circuit data generated by Quartus® Prime is transferred from the personal computer to the FPGA in order to actually operate the FPGA on the development board. This is called “programming” (also known as downloading).

Users can program the FPGA using the Altera® FPGA download cable USB-Blaster™ II and a utility called Programmer that comes with Quartus® Prime.

Many FPGAs use SRAM as a program element, so a non-volatile memory for boot memory must be prepared on the board. Altera® calls the non-volatile memory device "configuration ROM" and programs this memory. The FPGA only operates when data is transferred from this configuration ROM on the board. This is called "configuration".

The only exception is the MAX® 10 FPGA family. MAX® 10 is a new type of FPGA that has a built-in boot memory on a single chip. Therefore, MAX® 10 does not require an external boot memory.

9. Actual equipment verification

After powering the board back on and successfully transferring data from the configuration ROM to the FPGA, we move on to the phase of verifying the operation of the FPGA.

When there is a malfunction, signal verification is generally performed with a logic analyzer or oscilloscope, but for simple signal verification, Quartus® Prime has an on-chip debugging function called Signal Tap. This is a debugging method (mechanism) that configures a logic analyzer inside Altera® FPGA, and does not require any special equipment. All you need is a PC with Quartus® Prime installed, a board with the FPGA to be verified, and a download cable USB-Blaster™ II, and you can start debugging right away. SignalTap can be used without a license and can also be used with the free Quartus® Prime Lite Edition.

Signal Tap についてざっくり知りたい人、やってみたい人は、以下の記事をご覧ください。

For more information about Signal Tap, please refer to the manufacturer's documentation below and the free online training available on the manufacturer's website.

- Design Debugging with the Signal Tap Logic Analyzer (Quartus Prime Standard Edition)

- Design Debugging with the Signal Tap Logic Analyzer (Quartus Prime Pro Edition)

なお、オンライン・トレーニングの受講方法は、下記コンテンツをご覧ください。

10. Mass production

実機検証が完了すれば すぐに量産へ移ることができます。

The above is the general flow of FPGA development.

Let's give it a try!

However, if you have no experience with FPGA development, it would be foolhardy to start by coming up with specifications. Let's start by imitating it.

Evaluation boards released by Altera® and Mpression (Macnica 's original brand) come with reference designs (sample designs) and user guides (manuals). You can download sample design data from the evaluation board listing page on the website before or after purchase, or even if you don't purchase the board.

There are other ways to get sample designs other than the evaluation board page. For details, please see the content below.

Even if you do not yet have an evaluation board on hand, you can immediately begin steps 3 to 7.

First, get familiar with how to use the tools.

It is no exaggeration to say that mastering Quartus® Prime is the shortcut to FPGA development.

To get up and running quickly, we recommend instructor-led training.

If you have any questions, please contact our staff or use the inquiry form for semiconductor products.

This series of "The Real Introduction" will end in the next installment. In the final installment, "Part 5," I will introduce some useful websites for studying FPGAs and CPLDs.

Note:

本記事では 読者に親しんでいただくためメーカーサイトは日本語ページをご案内していますが、併せて英語ページも必ずご確認ください。日本語ページは情報の更新が遅れる場合がありますので注意してください。サイト内の言語切り替えは、ページ下の REGION(地域)により行えます。なお、言語を切り替えてもすべてのページが日本語になるわけではありませんのでご了承ください。

Click here for recommended articles

ほんとのほんとの導入編 その1. FPGA 開発をはじめるための環境づくり

ほんとのほんとの導入編 その2. FPGA 開発をはじめるために準備するもの

ほんとのほんとの導入編 その3. FPGA 開発をはじめるために必要な知識

ほんとのほんとの導入編 その4. FPGA 開発の流れ

ほんとのほんとの導入編 その5. 役立つコンテンツの紹介